Panel driving circuit, control method and panel

A technology of panel drive circuit and GIP circuit, which is applied in the direction of instruments, static indicators, etc., can solve the problems of large occupied area of GIP circuit area, difficult panel ultra-narrow border, uneven brightness around the periphery, etc., to achieve better display effect and realize narrow Frame requirements, the effect of increasing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

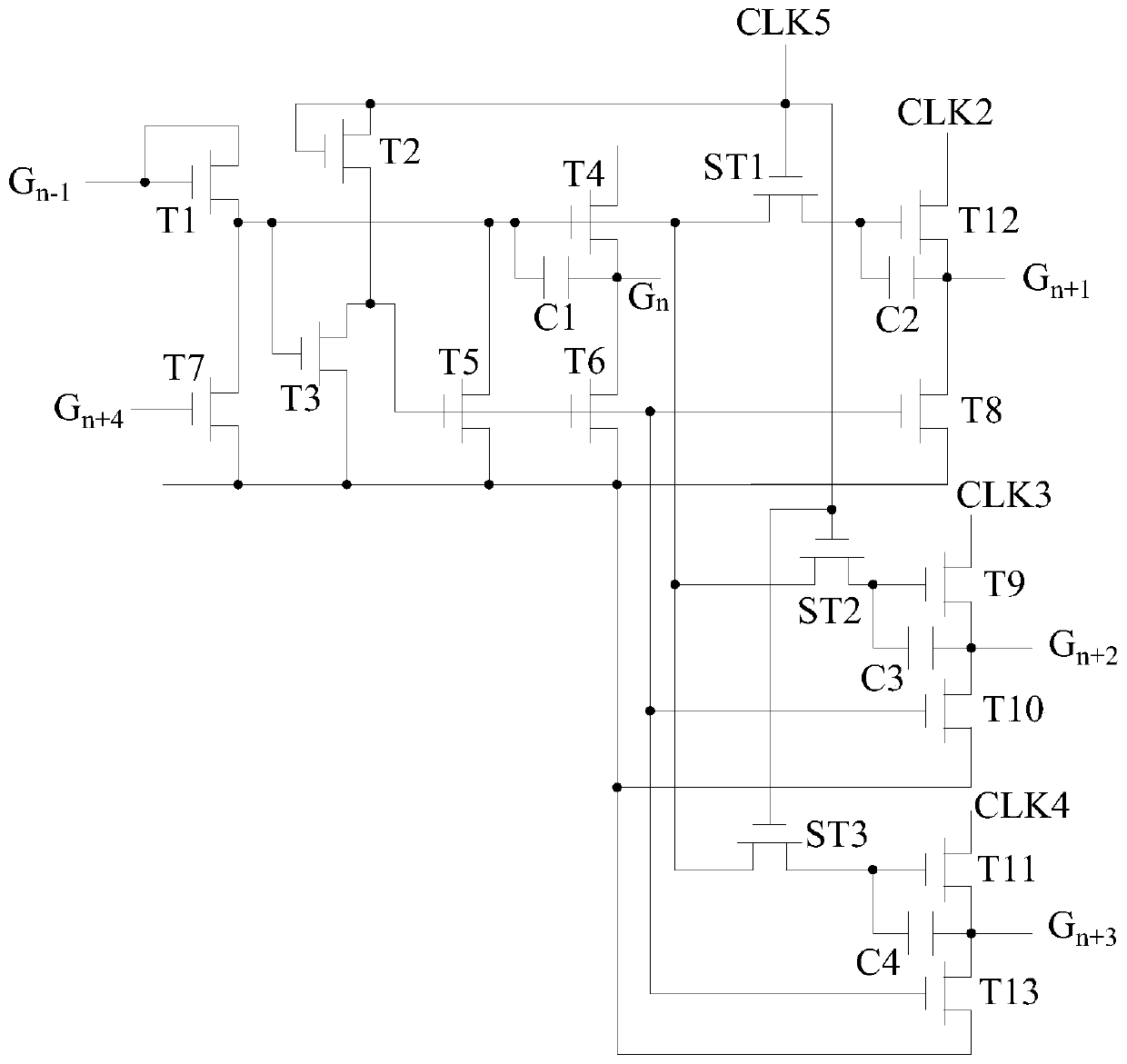

[0050] Please refer to figure 1 , Embodiment 1 of the present invention is:

[0051] A panel drive circuit, comprising a first GIP circuit, a second GIP circuit and a third GIP circuit, the structure of the second GIP circuit is the same as that of the third GIP circuit, and the first GIP circuit and the second GIP circuit are respectively The circuit is electrically connected to the third GIP circuit, the second GIP circuit is electrically connected to the third GIP circuit, and the first GIP circuit includes a transistor T1, a transistor T2, a transistor T3, a transistor T4, a transistor T5, a transistor T6, and a transistor T7 , transistor T8, transistor T12, transistor ST1, capacitor C1 and capacitor C2, the second GIP circuit includes transistor T9, transistor T10, transistor ST2 and capacitor C3;

[0052] The gate of the transistor T1 is electrically connected to the drain of the transistor T1 and the first scanning signal line, and the source of the transistor T1 is re...

Embodiment 2

[0075] Please refer to Image 6 , the second embodiment of the present invention is:

[0076] Please refer to Image 6, a method for controlling a panel drive circuit, comprising the following steps:

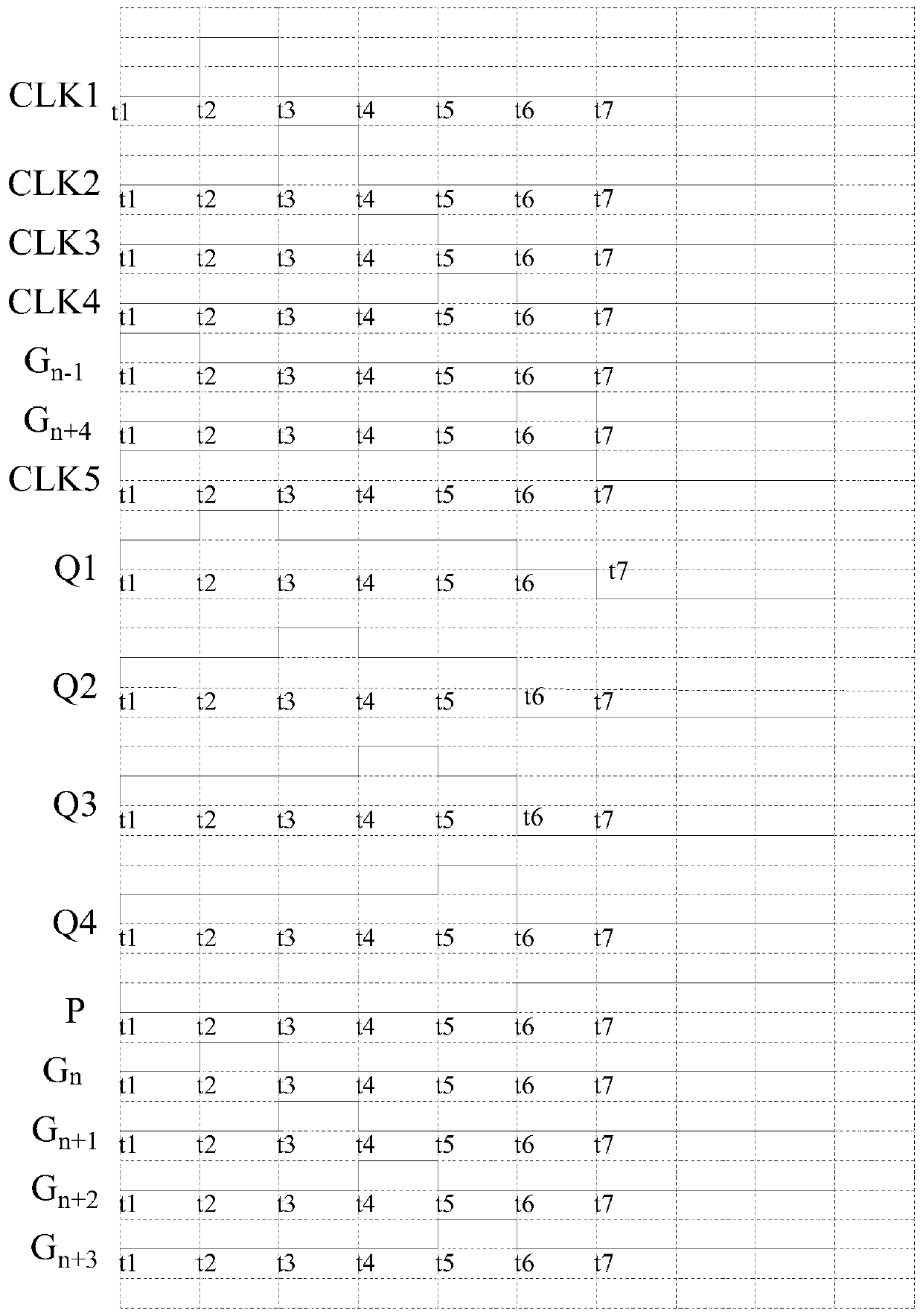

[0077] Step S1, in the first period of time, both the gate of the control transistor T1 and the gate of the transistor ST1 input a high level, and the drain of the control transistor T4, the gate of the transistor T7, the drain of the transistor T9 and the drain of the transistor T12 Very average input low level;

[0078] Step S2, in the second time period, both the drain of the control transistor T4 and the gate of the transistor ST1 are input with a high level, and the gate of the transistor T1, the gate of the transistor T7, the drain of the transistor T9 and the drain of the transistor T12 are controlled Very average input low level;

[0079] Step S3, in the third period of time, both the drain of the control transistor T12 and the gate of the transistor ST1 input a high...

Embodiment 3

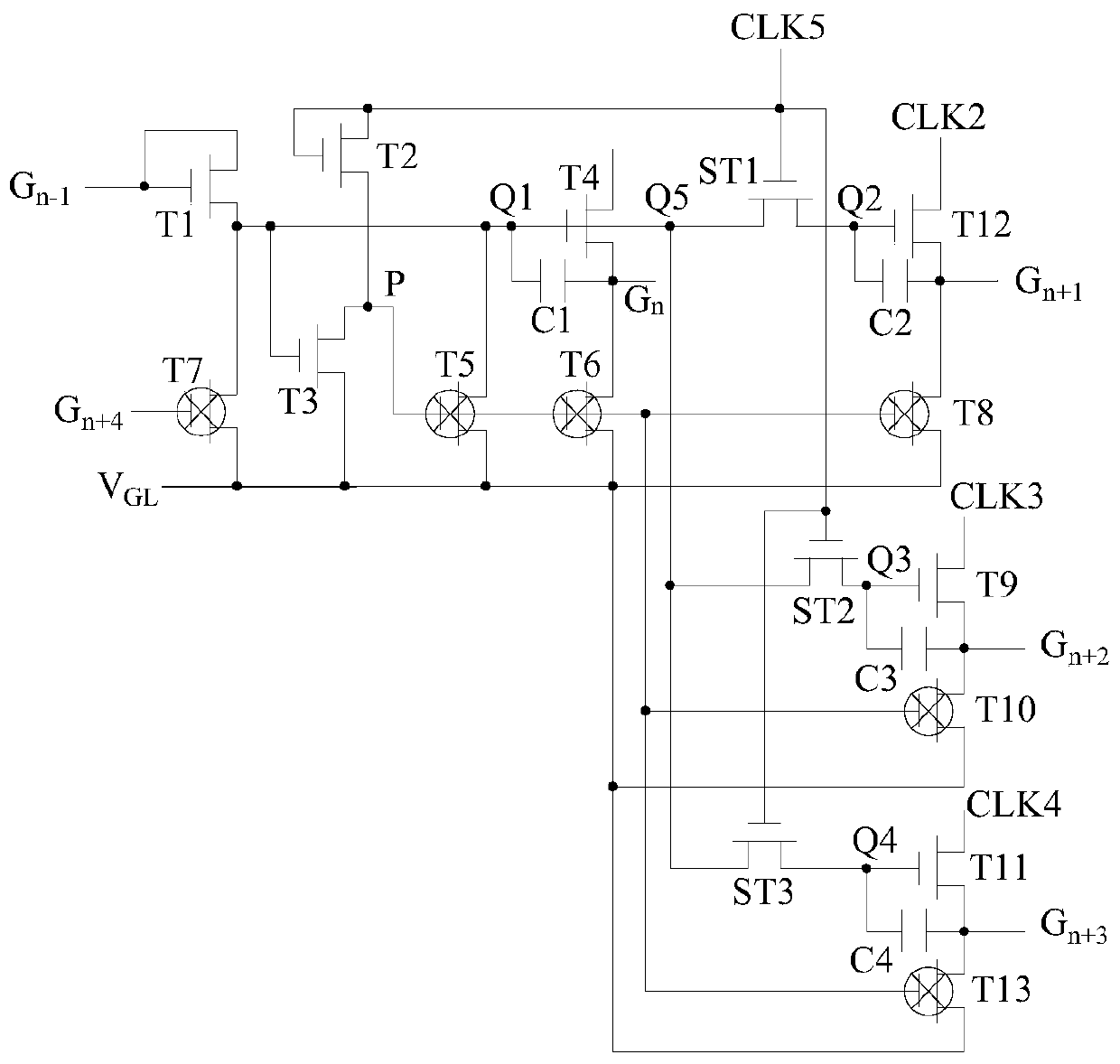

[0083] Please refer to Figure 7 , Embodiment three of the present invention is:

[0084] A panel includes a display area 1 and a non-display area 2, the non-display area 2 is distributed on both sides of the display area 1, and the non-display area 2 includes a panel driving circuit.

[0085] The panel designed in this scheme has a node-sharing structure for pull-up and pull-down nodes, all pull-down TFTs (transistor T5, transistor T6, transistor T8, transistor T10, and transistor T13) are connected to a P node, and all pull-up nodes (Q1, Q2, Q3, Q4, and Q5) make Q1, Q2, Q3, Q4, and Q5 independent of each other through 3 separate TFTs (transistor ST1, transistor ST2, and transistor ST3). There is no difference between the separate TFT and other TFTs. It is used to distinguish the name. The gates of these three separated TFTs are controlled by the clock signal CLK5 (clock signal name, no real meaning), and are connected in parallel to reduce the lateral length of the driving ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com