A Method for Realizing Data Consistency Based on Advance Update

An implementation method and consistent technology, which is applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve the problems of large read and write delays of the main memory, take a long time, and cannot fully utilize the performance of DMA, etc., so as to alleviate the delay Problems, Effects of Efficiency Improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] This embodiment provides a method for implementing data consistency based on early update, which is applied to a multi-core processor system. During the implementation process, a counter is added for each L1 DCache and the Cacheline of other levels of Cache to record the number of dirty data copies. Cacheline access status, write the copy containing dirty data back to the main memory in advance, effectively alleviate the delay problem caused by the Cache refresh operation before DMA transfer data, and improve the efficiency of the DMA transfer system.

[0050] The maximum value that the counter that the present invention increases can record is the Cacheline quantity N of current Cache, promptly the bit width of counter is [log 2 N-1,0]. A multi-core processor system contains at least two CPUs,

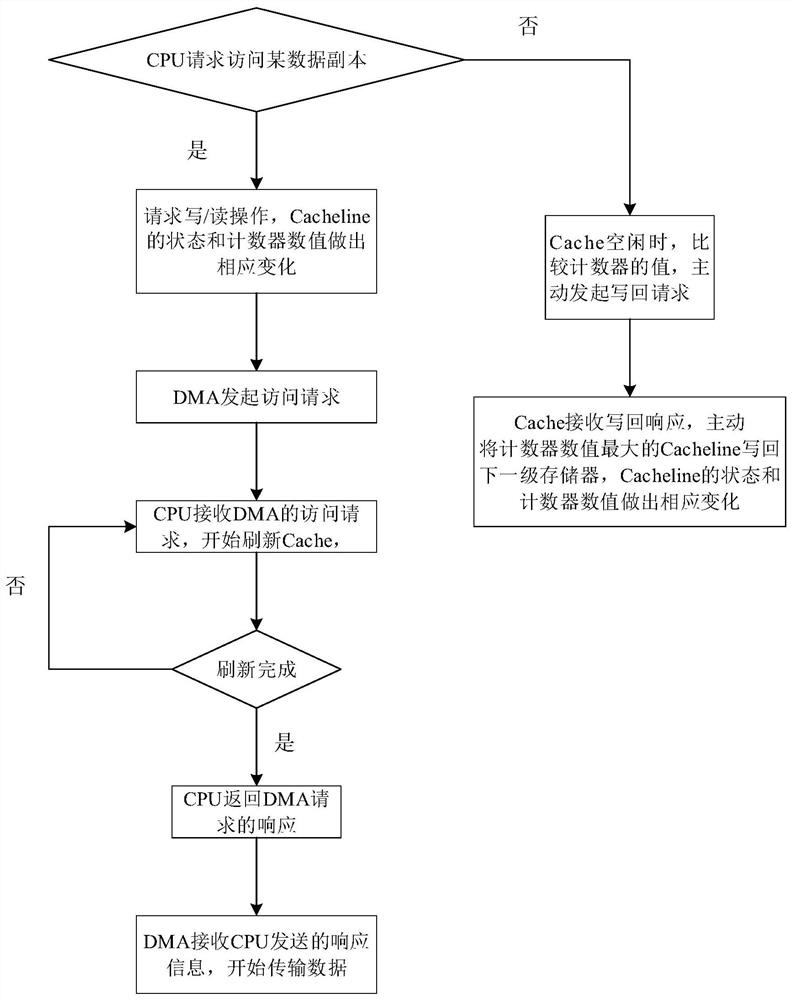

[0051] see figure 1 , the method includes:

[0052] Step 1. The first CPU requests to access a certain data copy, and the first CPU is any CPU in the multi-core processor sy...

Embodiment 2

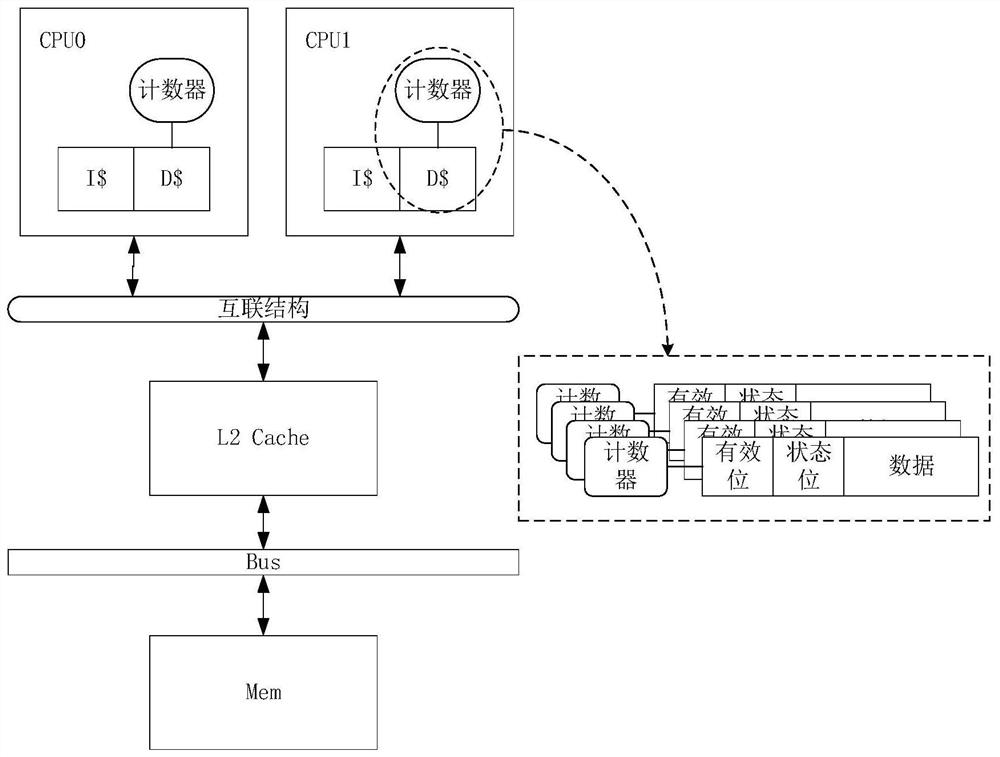

[0070] This embodiment provides a description of the practical application of the method for realizing data consistency based on early update described in Embodiment 1, see figure 2 ,details as follows:

[0071] In this embodiment, the hardware device includes a multi-core processor system, and the multi-core processor system includes CPU0, CPU1, a second-level shared high-speed cache (L2 Cache), a bus (Bus), a main memory (Mem) and an interconnection structure. Among them, each CPU adopts Haval structure, including a 32kB instruction cache (ICache) and data cache (DCache).

[0072] The L1 DCache adopts a 4-way set associative organizational structure, the number of groups is 64, and the cacheline size is 128 bytes. Therefore, the maximum value N that can be recorded by the counter corresponding to the dirty cacheline of the L1 DCache is 256.

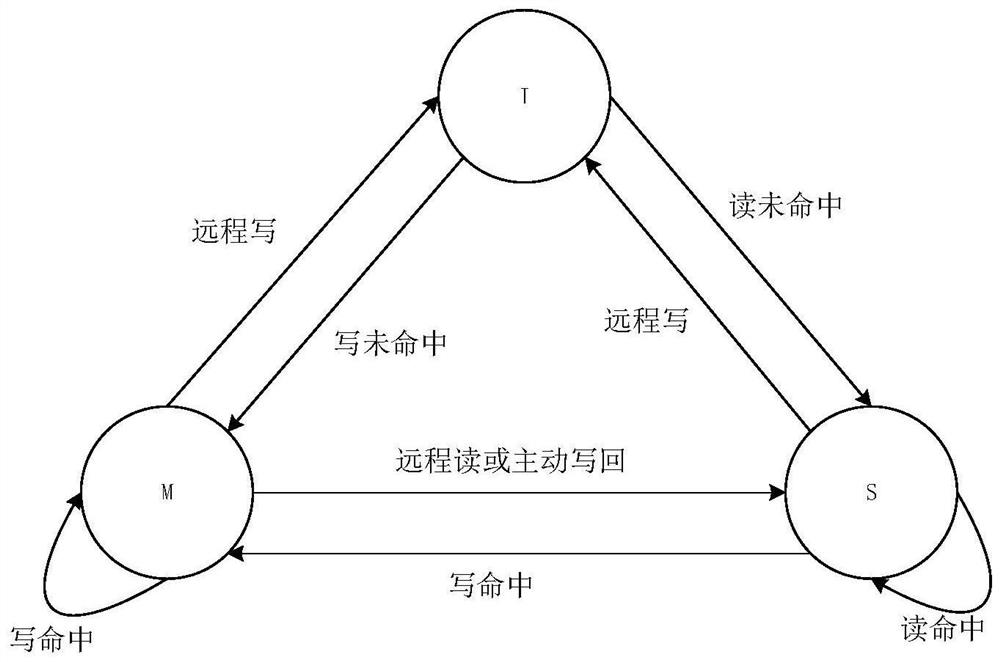

[0073] This embodiment is based on the write-back method and the write invalidation strategy, and uses the MSI protocol (Modified Sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com