System and method for realizing chip testing

A chip testing and chip technology, applied in the field of systems for realizing chip testing, can solve problems such as many pins, large area, and increased testing costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] In order to describe the technical content of the present invention more clearly, further description will be given below in conjunction with specific embodiments.

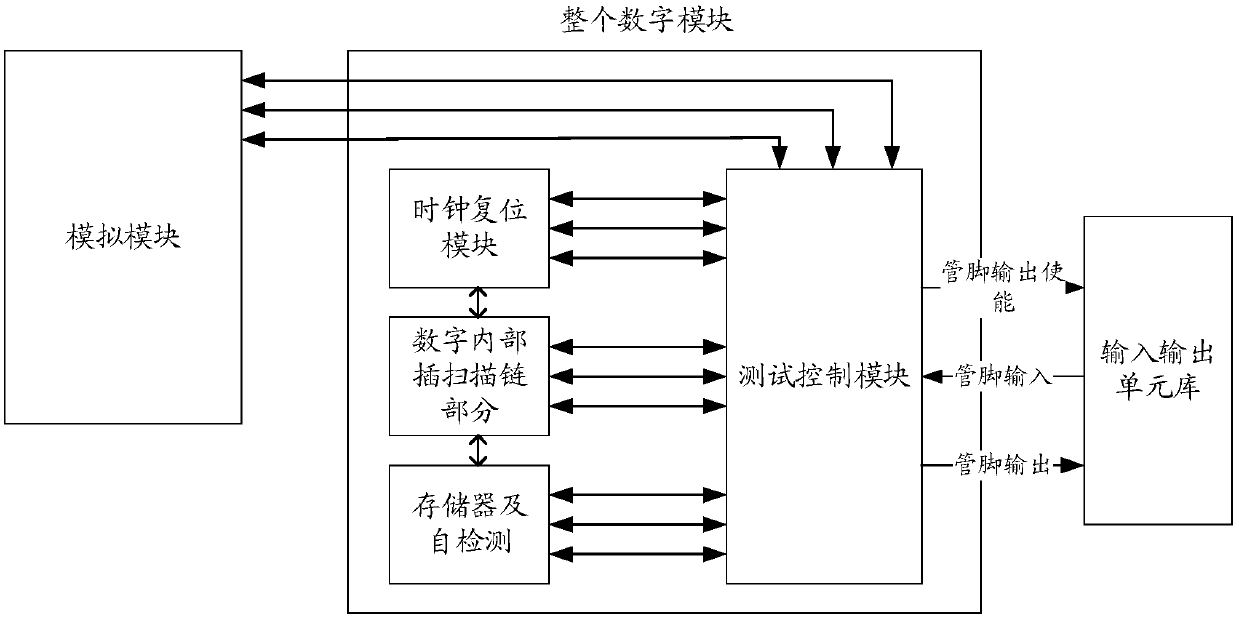

[0048] The system for implementing chip testing of the present invention, wherein the system includes:

[0049] Analog IP module, used for analog IP testing;

[0050] A digital module, connected to the analog IP module, is used for testing internal communication signals;

[0051] The input and output unit library is connected with the digital module and is used to package the connection line;

[0052] The test module is connected with the analog IP module, the digital module and the input and output unit library, and is used for testing the chip;

[0053] The test module includes control pins, and the control pins are connected with the input-output unit library via the pins of the input-output unit library, and are used to control different test modes of the chip.

[0054] As a preferred embodiment of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com