Method for quickly verifying correct connection of FPGA interconnection lines

An interconnection line, the correct technology, applied in the field of electronics, can solve the problems of slow speed, short circuit and open circuit of interconnection lines, low coverage, etc., to achieve the effect of improving verification speed and improving design speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The method for quickly verifying the correct connection of FPGA interconnection lines proposed by the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

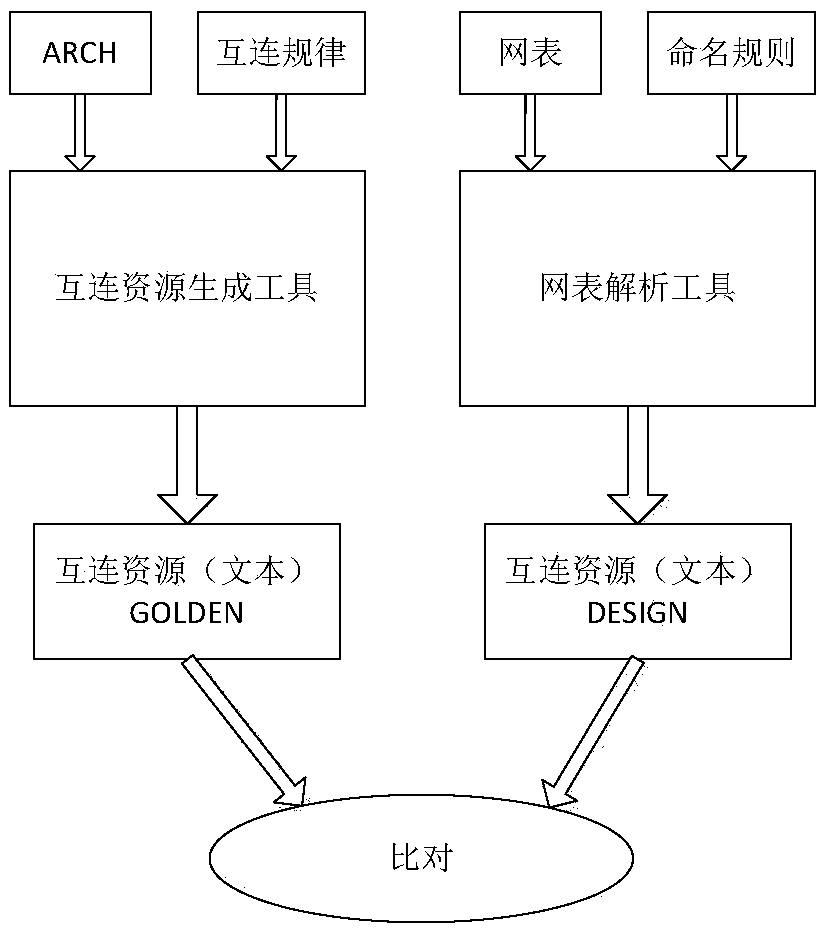

[0020] Such as figure 1 As shown, it is the overall flowchart of the verification method proposed by the present invention. As can be seen from the figure, the method for quickly verifying the correct connection of the FPGA interconnection line proposed by the present invention mainly starts from two aspects. One is based on the interconnection rules and The ARCH file information of the designed chip is used to generate the interconnection resource file as the GOLDEN model. The second is to analyze the designed chip netlist to obtain the interconnection resource file corresponding to the actual circuit. By comparing the files, the verification of the interconnection correctness of the actual design circuit can be realized.

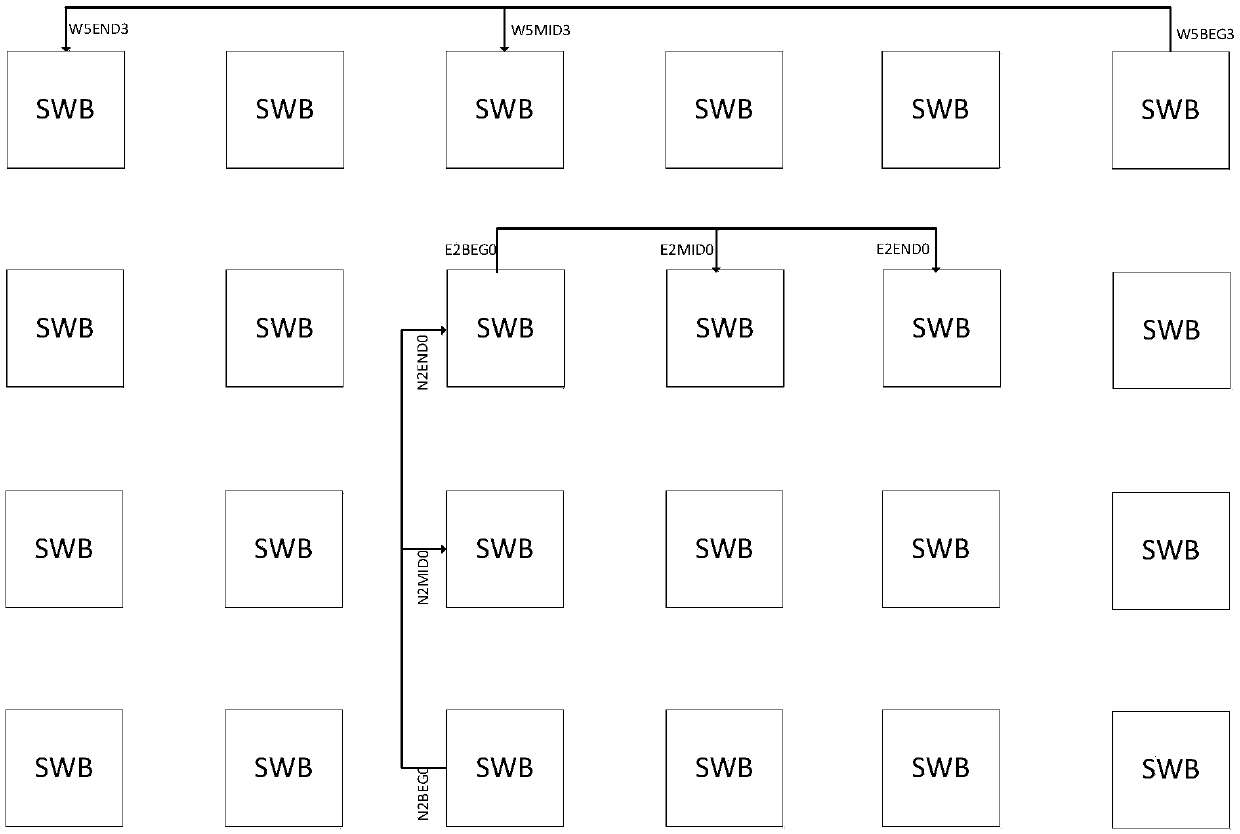

[0021] In order to obtain the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com