Vertical structure chip preparation method

A vertical structure and chip technology, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve problems such as leakage, chips are easily affected by the external environment, etc., and achieve the effect of improving reliability and reducing the impact of leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

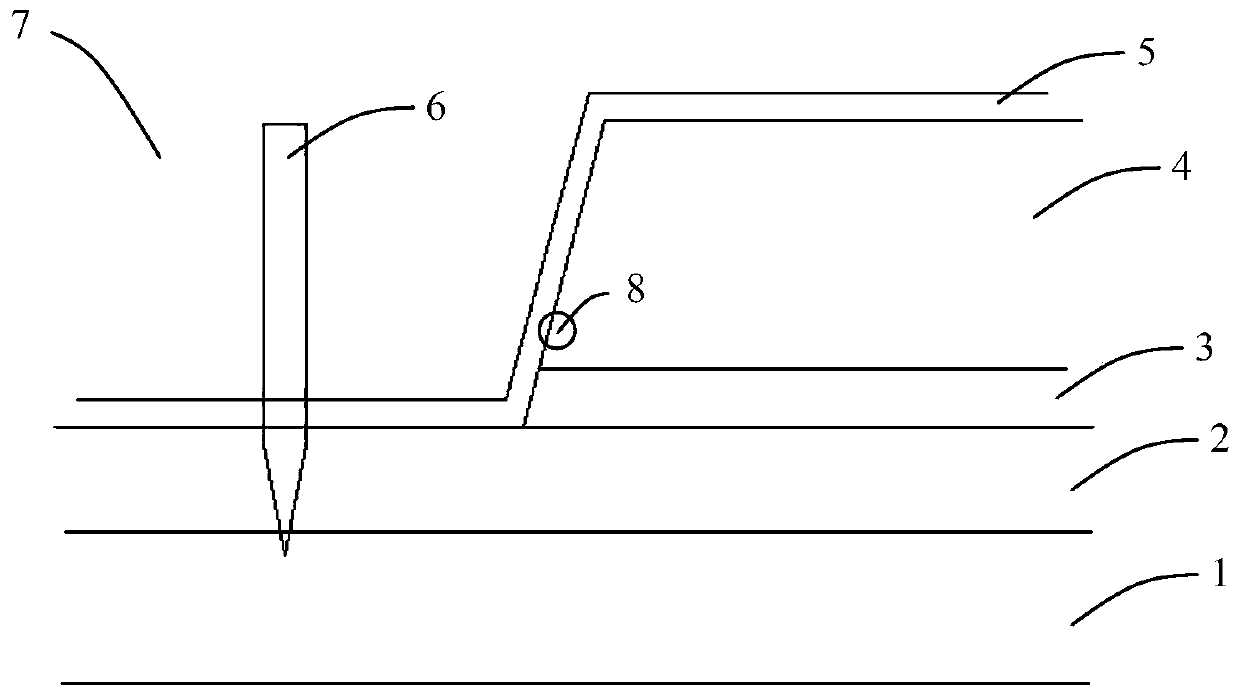

[0018] In order to more clearly illustrate the implementation cases of the present invention or the technical solutions in the prior art, the specific implementation manners of the present invention will be described below with reference to the accompanying drawings. Obviously, the accompanying drawings in the following description are only some embodiments of the present invention, and those skilled in the art can obtain other accompanying drawings based on these drawings and obtain other implementations.

[0019] Aiming at the problems existing in the preparation process of the existing vertical structure chip, the present invention provides a new vertical structure chip preparation method, including:

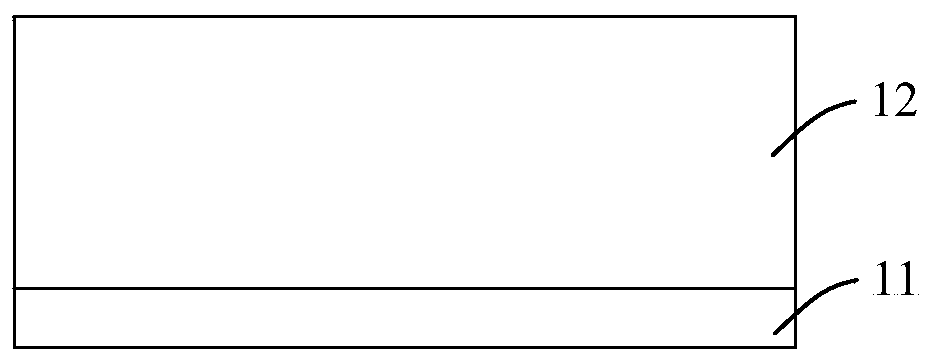

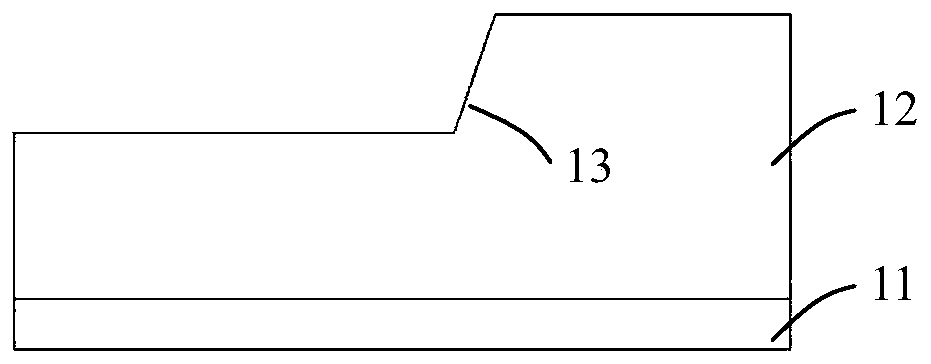

[0020] S1 sequentially grows a GaN structure 12 on the growth substrate 11, including an N-type GaN layer, a quantum well layer and a P-type GaN layer, such as figure 2 shown. In this step, the growth substrate 11 can be silicon, sapphire, SiC, etc., which is selected acco...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com