Arithmetic lazy flags representation for emulation

A notation and arithmetic technique, applied in software simulation/interpretation/simulation, computing, instrumentation, etc., to solve problems such as reducing the expected performance, delay, and wasting clock cycles of simulation applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

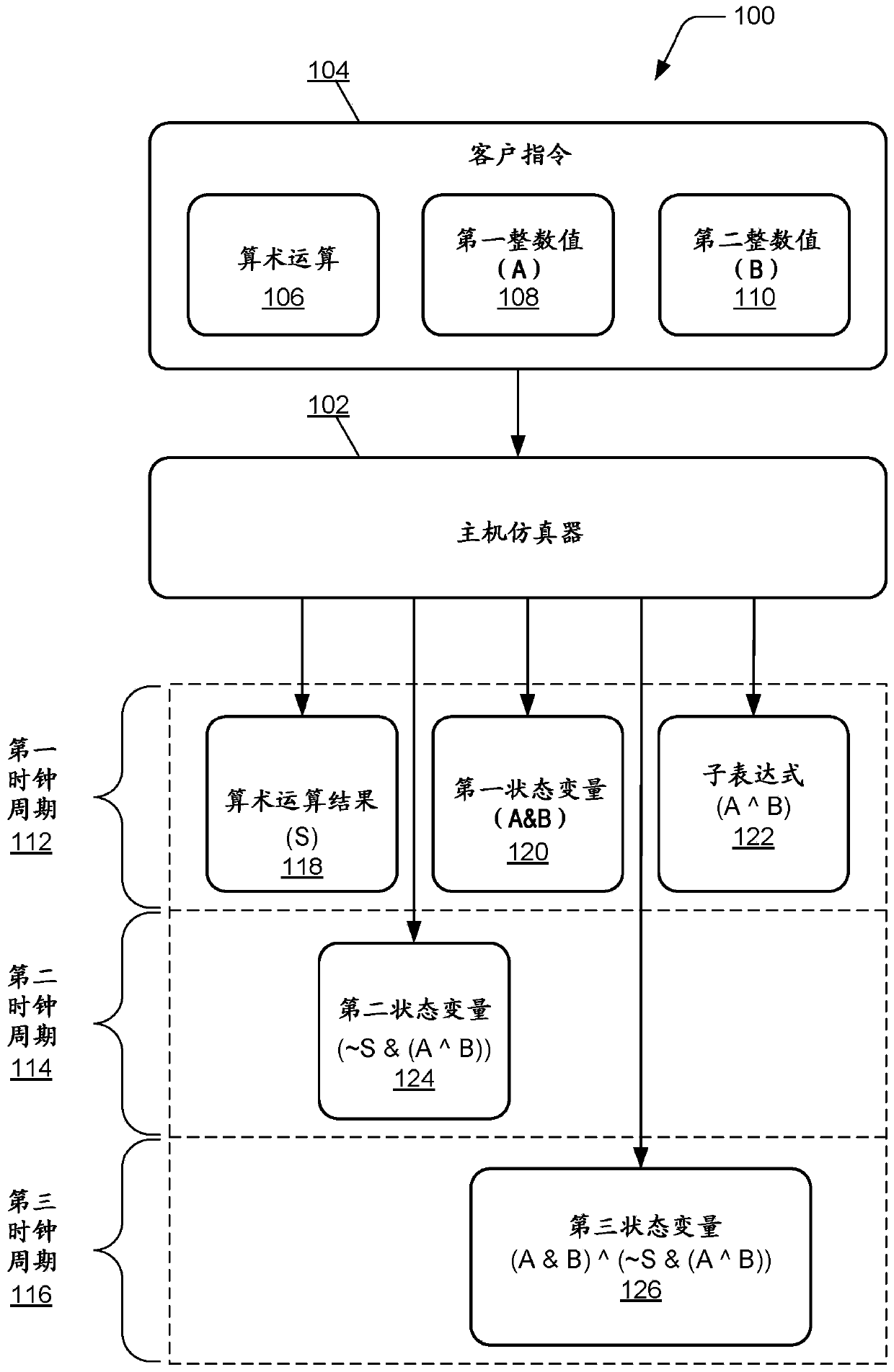

[0011] Aspects of arithmetic lazy flag representations for emulation are described for emulating arithmetic instructions designed to be executed by one processor system architecture to be executed by a different processing system architecture such that an application or operating system Can be run by a processor system even if the application or operating system is not designed to be run by the processor system. As used herein, the processor system performing the emulation is referred to as the "host processor system". Instructions received and emulated by the host processor system are called "guest instructions," which are designed to run on a different architecture of the guest processor system than that of the host processor system.

[0012] In an implementation, guest instructions require the use of information stored in certain memory locations of the processor system. For example, when an arithmetic operation of an application is performed by a computing device running ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com