A system and a method for quickly building an FPGA digital simulation model

A digital simulation and simulation model technology, applied in the field of FPGA software verification, can solve the problem of high cost of verification and testing labor and time, and achieve the effect of ensuring reusability, enhancing collaboration, and having good application prospects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

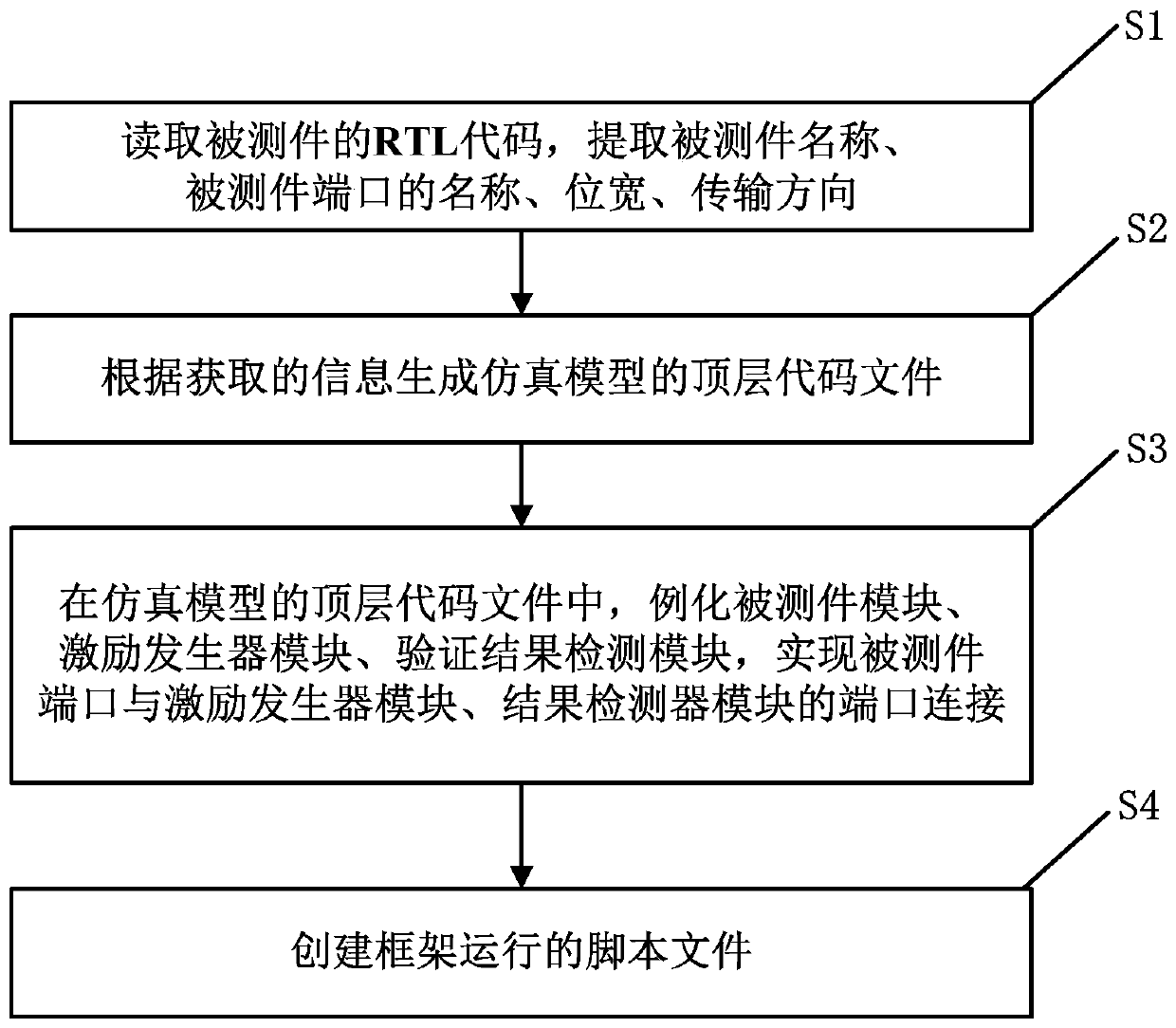

[0033] see figure 1 As shown, the embodiment of the present invention provides a kind of method that quickly builds FPGA digital simulation model, comprises the following steps:

[0034] S1, read the RTL code of the DUT, extract the name of the DUT, the name of the DUT port, bit width, and transmission direction;

[0035] S2, generating a top-level code file of the simulation model according to the acquired information;

[0036] S3, in the top-level code file of the simulation model, instantiate the module under test, the excitation generator module, and the verification result detection module, and realize the connection between the port of the module under test and the port of the excitation generator module and the result detector module; The detector module is used to generate excitation signals, and the verification result dete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com