Enhanced phase-locked loop for single-phase power grid voltage synchronization information detection

A grid voltage and synchronization information technology, applied in the field of phase-locked loops, can solve problems such as difficult to accurately estimate grid amplitude, frequency and phase angle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

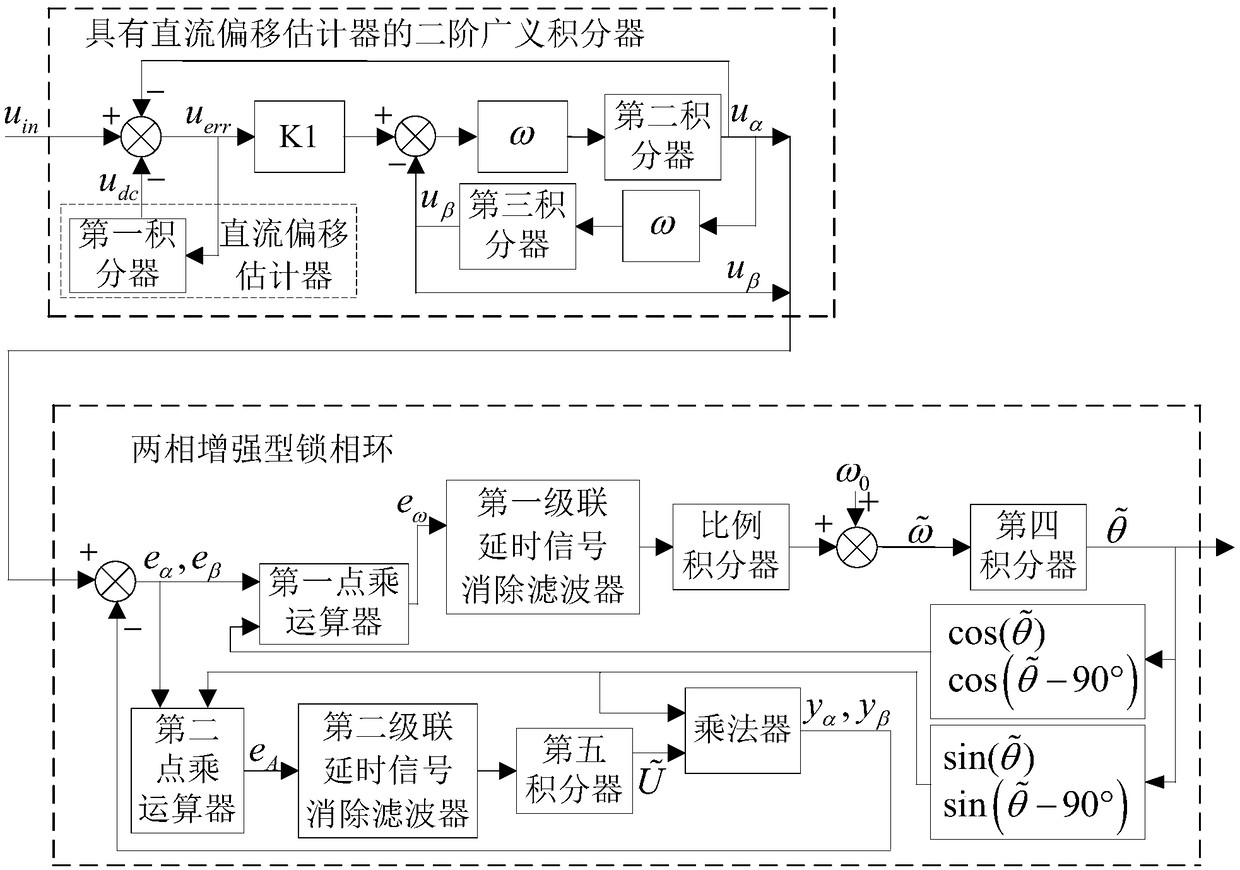

[0033] Specific implementation mode 1: the following combination figure 1 To explain this embodiment, the enhanced phase-locked loop used for the detection of single-phase grid voltage synchronization information described in this embodiment is:

[0034] Input the single-phase grid voltage to the second-order generalized integrator with DC offset estimator to obtain the filtered value and quadrature signal of the input grid voltage without DC offset;

[0035] Input the obtained filtered value and quadrature signal to the two-phase enhanced phase-locked loop to obtain the online estimation value of the amplitude, frequency and phase angle of the single-phase grid voltage;

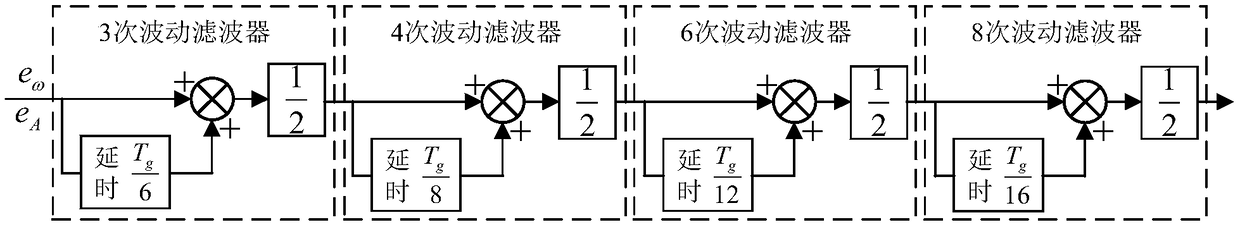

[0036] In the frequency estimation loop and amplitude estimation loop of the two-phase enhanced phase-locked loop, the first cascade delay signal elimination filter and the second cascade delay signal elimination filter are respectively added to eliminate the input harmonics to the estimation result Impact.

specific Embodiment approach 2

[0037] Specific implementation manner 2: the following combination figure 1 To explain this embodiment, this embodiment will further explain the first embodiment. The specific process of obtaining the filtered value of the input grid voltage and the quadrature signal without DC offset is as follows:

[0038] Step 1. At the beginning of the estimation period, collect the single-phase grid voltage u in , Minus the filtering value u of the last estimation period α And the estimated DC offset u of the previous estimation period dc After that, the filtering error u of this estimation period is obtained err ;

[0039] The filtering error of this estimation period u err Input to the first integrator in the DC offset estimator to obtain the DC offset estimation value u for this estimation period dc ;

[0040] Step 2. The filtering error u of the estimation period obtained in step 1 err Multiply by the factor K 1 , Minus the orthogonal signal u of the previous estimation period β , The diff...

specific Embodiment approach 3

[0042] Specific implementation manner three: the following combination figure 1 To explain this embodiment, this embodiment will further explain the second embodiment. The specific process of obtaining the online estimated values of the amplitude, frequency and phase angle of the single-phase grid voltage is as follows:

[0043] Step 3. The filtered value u of the estimation period obtained in step 2 α And the orthogonal signal u of the estimated period β Subtract the instantaneous estimated value y of the last estimation period respectively α And y β , Obtain the instantaneous value estimation error e of this estimation period α And e β ;

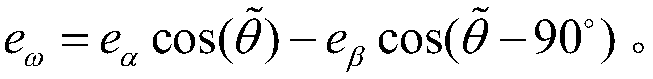

[0044] The instantaneous value estimation error of this estimation period e α And e β Input to the first dot product operator to calculate the frequency error e of the frequency estimation loop of the two-phase enhanced phase-locked loop ω ;

[0045] Frequency error of frequency estimation loop e ω Input to the first cascade delay signal elim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com