Chip and method for I2C bus expansion

A chip and bus technology, applied in the field of board card design, can solve the problems of ineffective protection of I2C signals, difficult wiring, high cost of external expansion chips, etc., to reduce board card density and design difficulty, reduce design cost, and prevent hanging dead effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the embodiments of the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

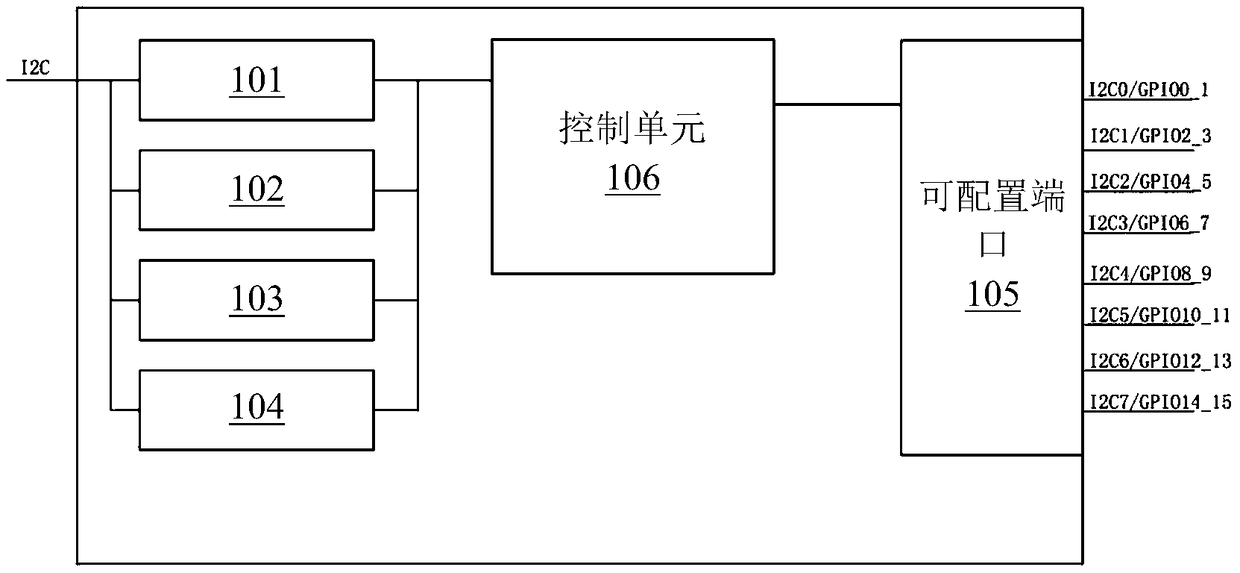

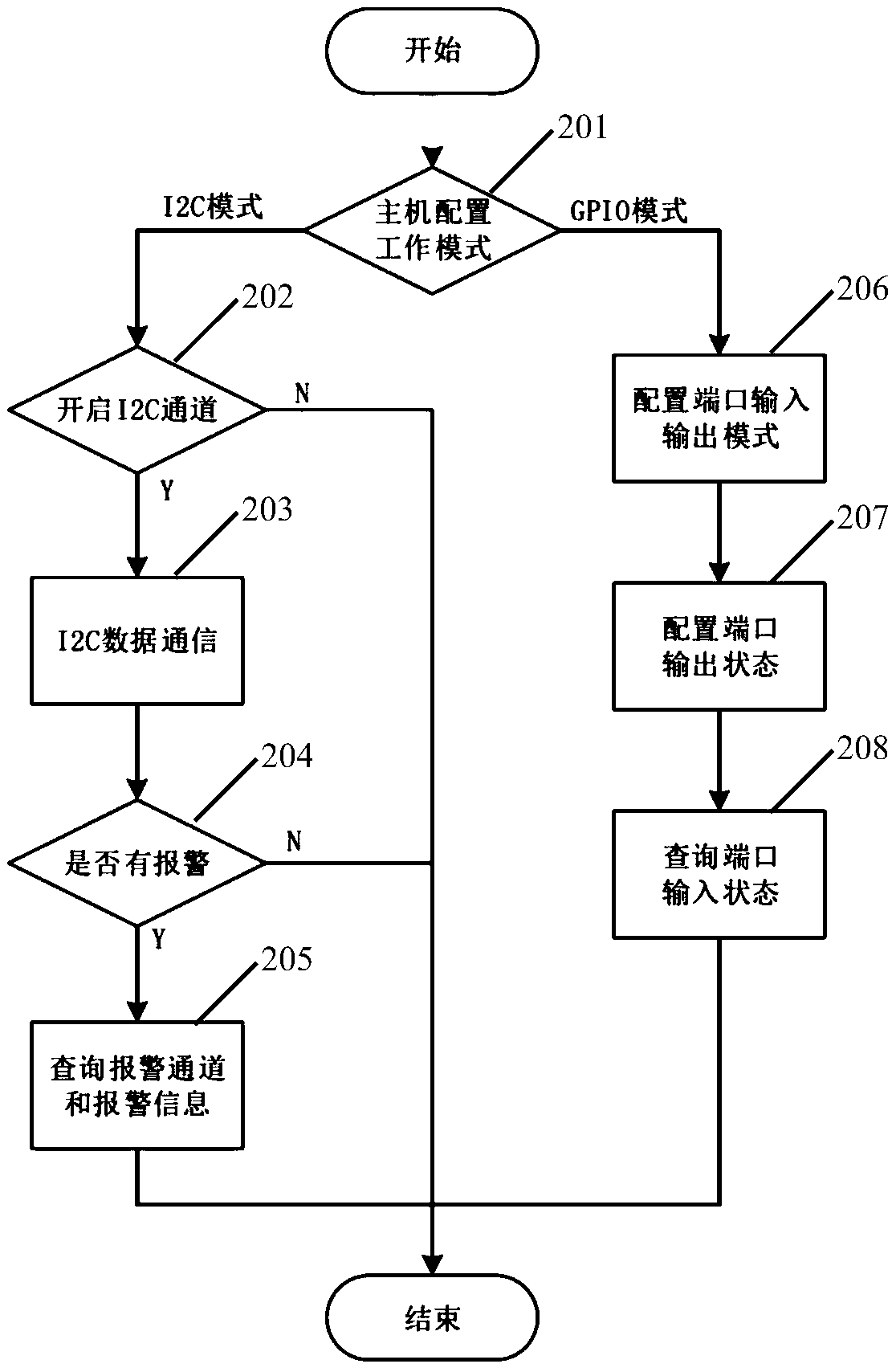

[0025] Based on the above purpose, the first aspect of the embodiments of the present invention proposes an embodiment of a chip for I2C bus extension. figure 1 Shown is a schematic of the chip.

[0026] Such as figure 1 As shown in , the chip may include: a register bank 101-104 for storing port configuration information; a configurable port 105, including multiple groups of I / O pins, each group having three I / O pins; and a control unit 106, respectively connected to the register groups 101-104 and the configurable port 105, for reading and writing register data and separately configuring the working mode and working state of each group of I / O pins according to the port configuration information. Amo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com