A high-speed and low-jitter frequency and phase detector and clock data recovery circuit

A clock data recovery, frequency and phase detector technology, applied in the direction of electrical components, power automatic control, etc., can solve the problems of unsuitable data signals, PFD complexity, etc., achieve a large capture range, reduce jitter, and improve tuning linearity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described below in conjunction with the accompanying drawings.

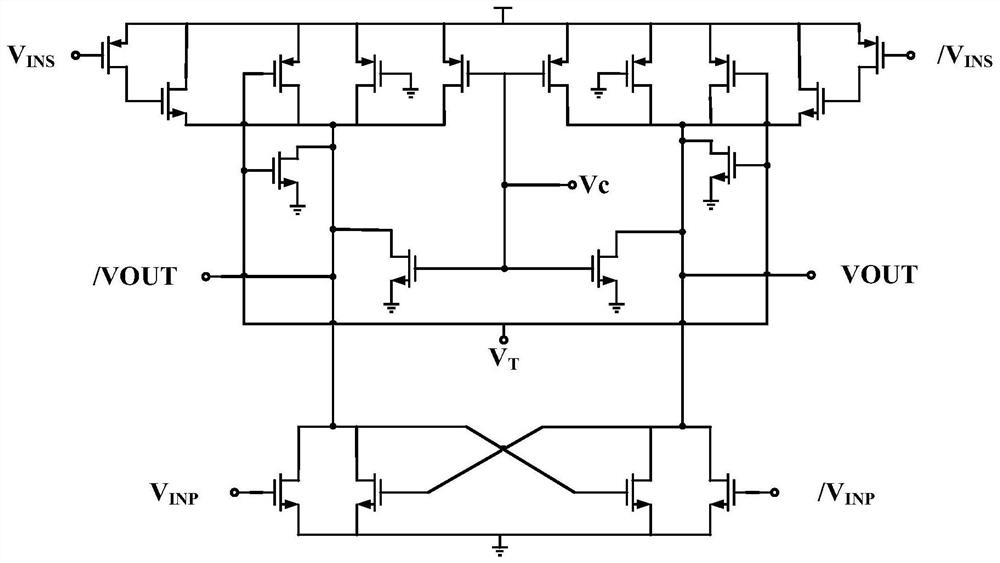

[0039] Such as figure 1 Shown is a brand-new frequency and phase detector, which can retain the fast frequency acquisition capability of Bang-Bang PFD, and can also obtain low jitter performance in the phase detection stage after frequency locking.

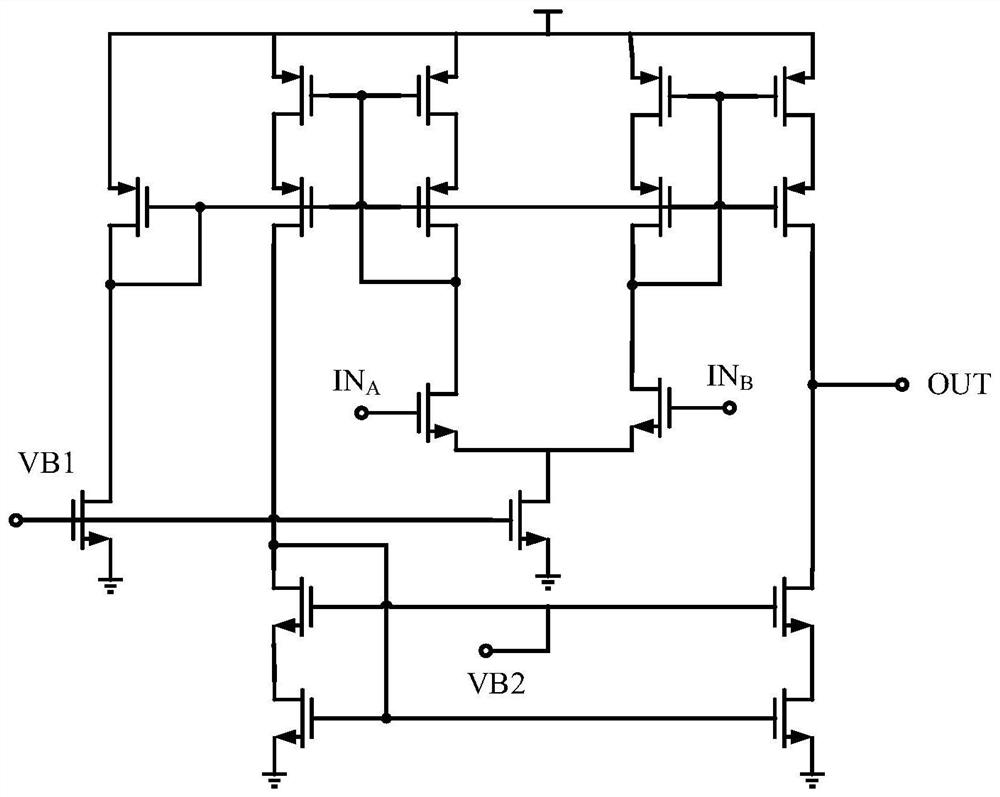

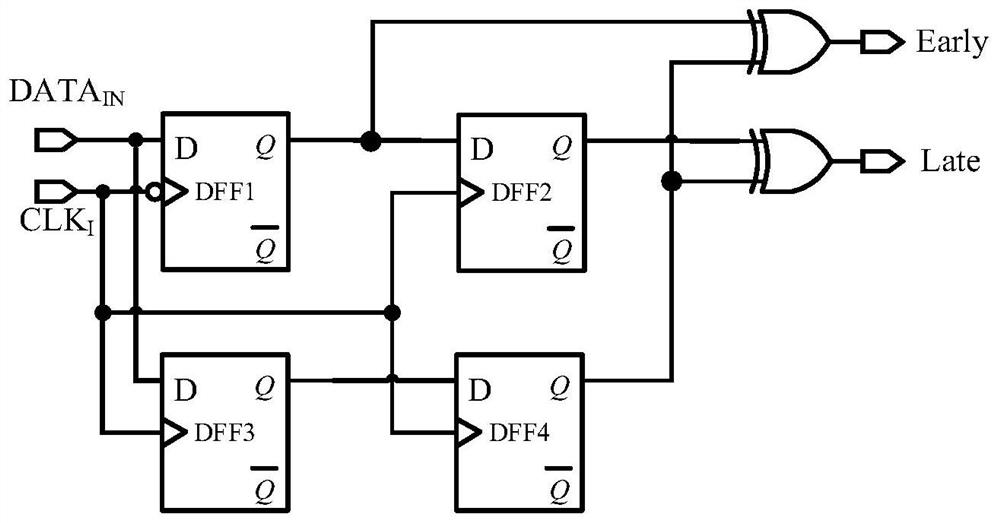

[0040] refer to Figure 7 It is a high-speed and low-jitter frequency and phase detector of the present invention. Frequency and phase detectors include Q-channel Bang-Bang-type PDs (DFF6, DFF7, DFF8), I-channel Bang-Bang-type PDs (DFF1, DFF3, DFF5), three-state output FD and two DFFs (DFF2 and DFF4 ), two XORs (used to form Alexander PD). Among them, the Bang-Bang type PD of Q road, DATA IN with CLK Q As the input signal of DFF6 and DFF7, CLK Q Connect to DFF6 in reverse. DFF8 samples the output of DFF6 on the falling edge of DFF7; DATA in the Bang-Bang type PD of I channel IN with CLK I As the input signal of D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com