High electrical performance chip packaging structure and manufacturing method

A technology with chip packaging structure and high electrical performance, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of inability to meet the application environment, large deformation of the solder mask, etc., to reduce the phenomenon of delamination, low cost, The effect of strong moisture resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

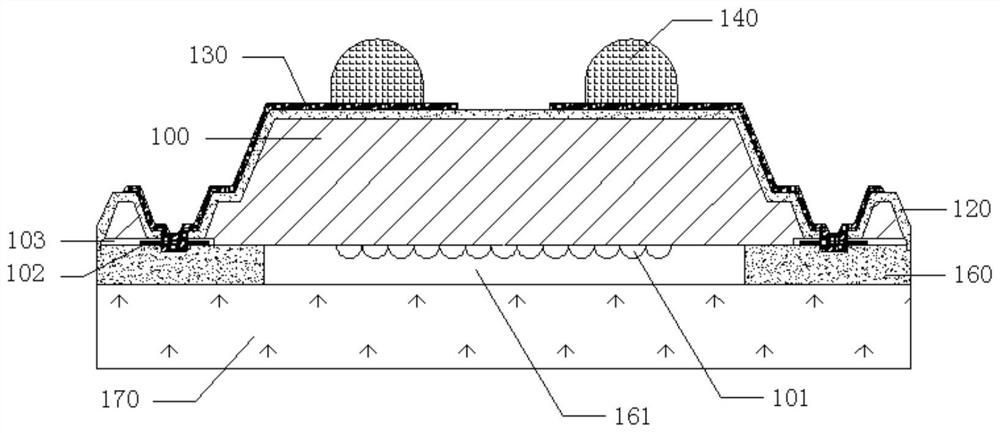

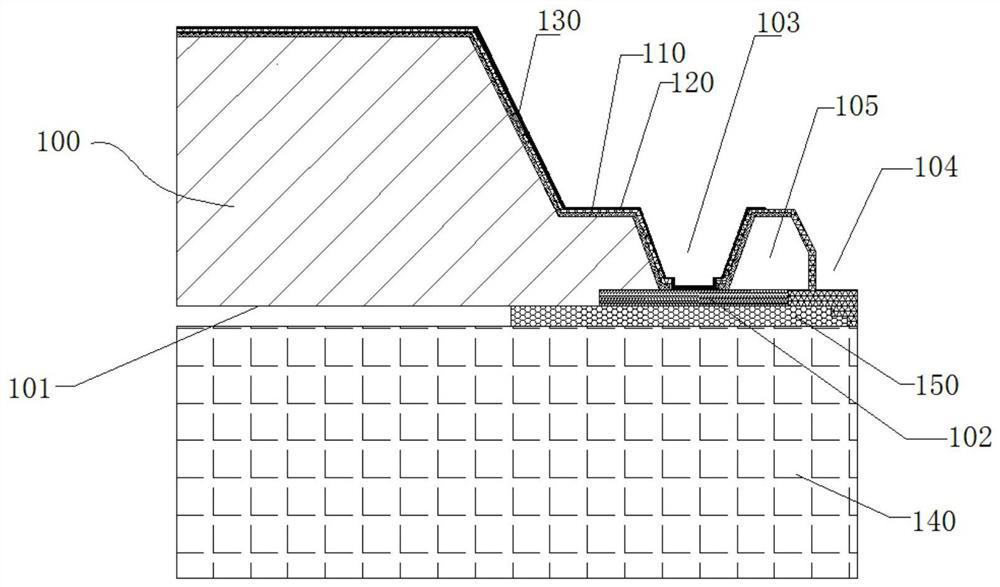

[0027] Such as figure 2As shown, a chip packaging structure with high electrical performance includes a chip 100, the front of the chip includes a functional area 101 and several soldering pads 102 located around the functional area, the front of the chip does not have a dielectric layer, and the chip The back of the substrate of the substrate is formed with a first opening 103 extending toward the pad, and the bottom of the first opening exposes the back of the pad, the back of the substrate of the chip and the sidewall of the first opening Two insulating layers 110, 120 are laid, wherein the inner insulating layer 110 is made of silicon dioxide or silicon nitride, and the outer insulating layer 120 is made of photoetching positive insulating glue. And the two layers of insulating layers extend and cover the edge of the back side of the exposed pad, and the outer layer of the insulating layer is laid with a metal wiring layer 130, and the metal wiring layer is electrically c...

Embodiment 2

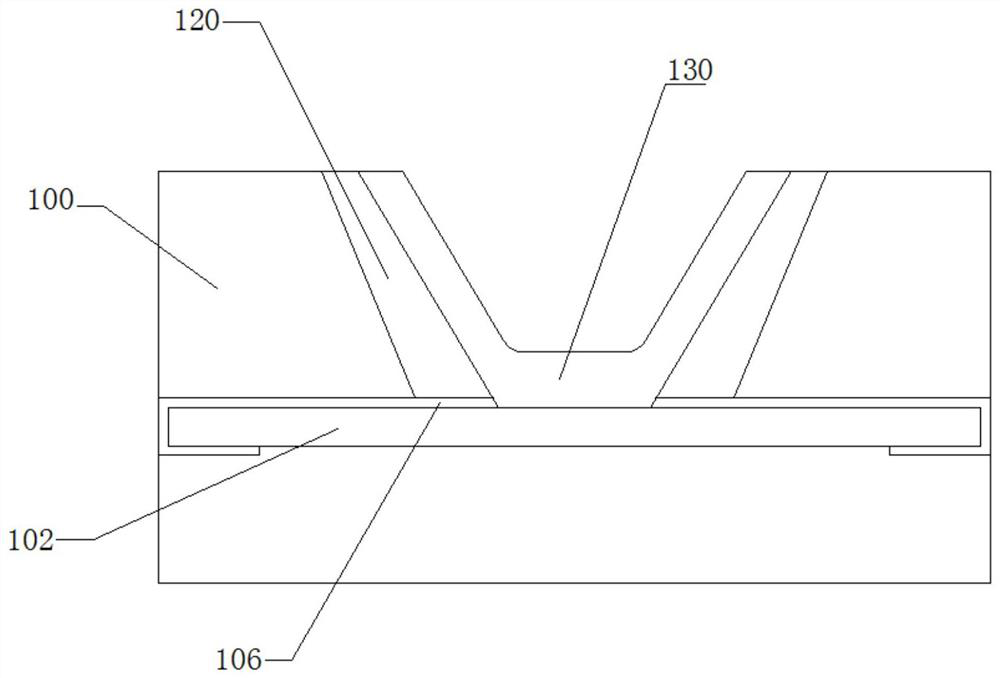

[0038] Such as image 3 with Figure 4 As shown, a chip packaging structure with high electrical performance includes a chip 100, the front side of the chip includes a functional area and several welding pads 102 located around the functional area, and a dielectric layer 106 is provided on the front side of the chip; The pad is located in the dielectric layer, and a part of the dielectric layer is separated between the pad and the substrate of the chip, and a first opening extending toward the pad is formed on the back of the substrate of the chip, and the first opening extends toward the pad. The bottom of an opening exposes the upper part of the dielectric layer on the back of the pad, and the exposed central part of the dielectric layer is hollowed out or completely hollowed out to form a second opening that exposes the back of the pad, exposing the When the central part of the dielectric layer is hollowed out, see image 3 A layer of insulating layer 120 or two layers of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com