ESD detection device, integrated circuit and method applied to digital integrated circuits

A technology of an integrated circuit and a detection method, which is applied to circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, emergency protection circuit devices, etc. Occupying resources and other problems, to achieve the effect of real-time ESD exceeding the limit, improving efficiency and real-time discovery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

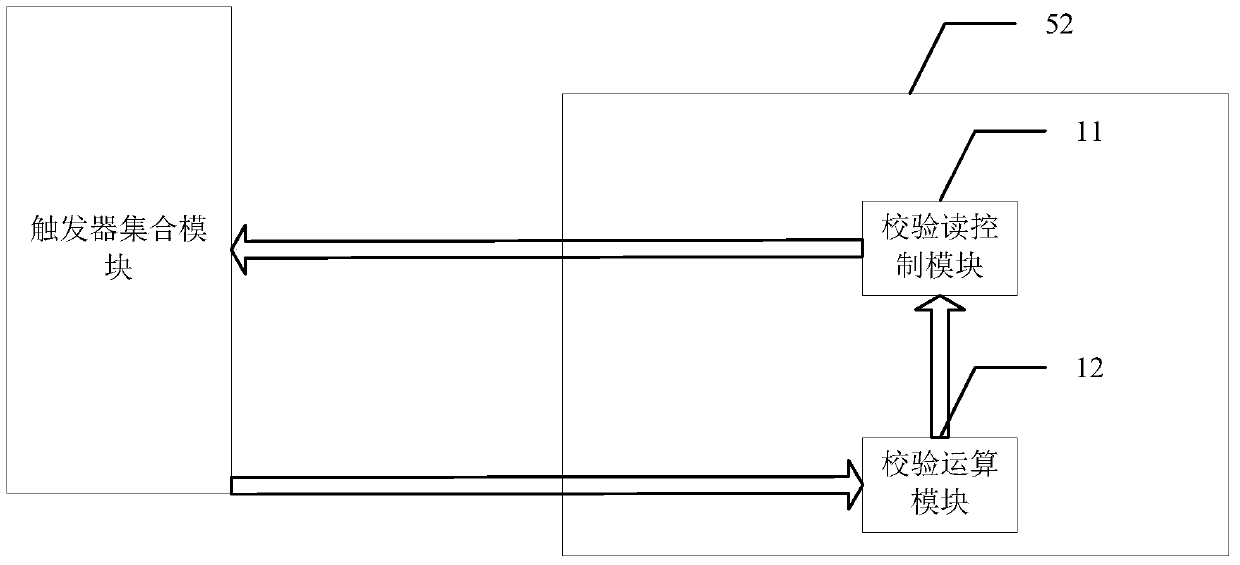

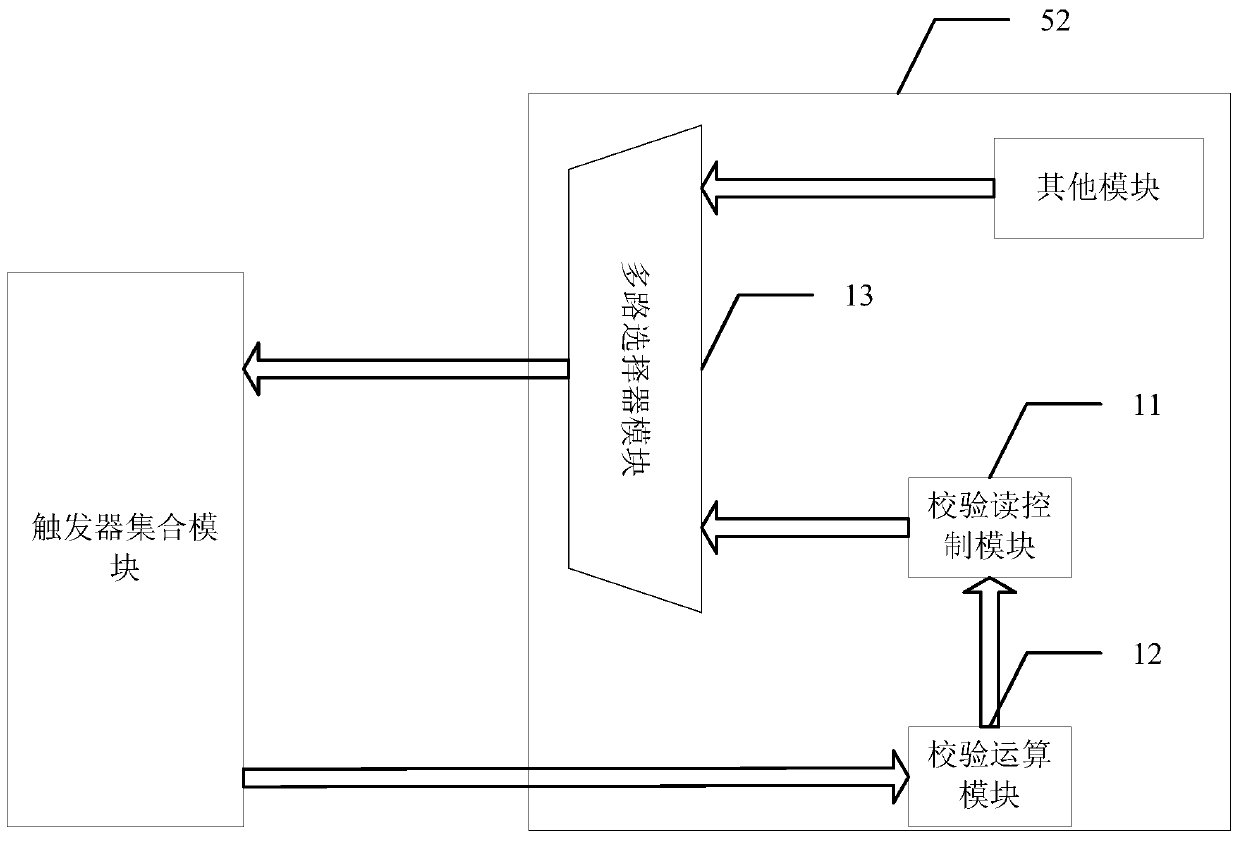

[0035] see figure 1 , the embodiment of the present application provides an ESD detection device applied to digital integrated circuits, including:

[0036] The verification read control module 11 is configured to initiate a read operation to the flip-flop set module.

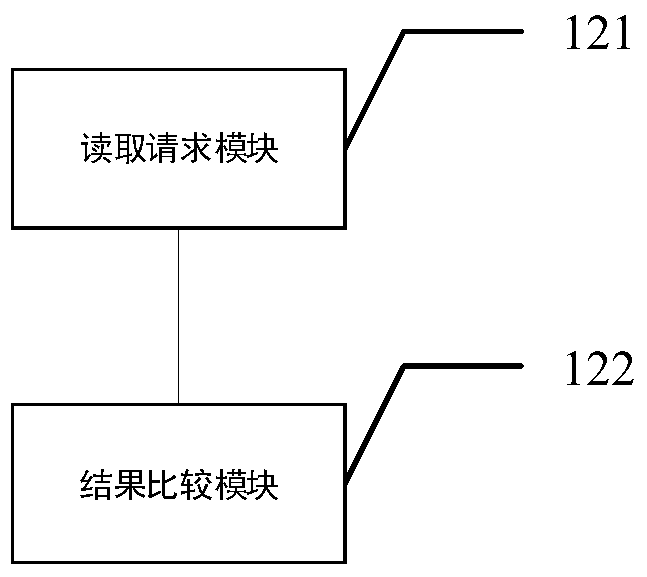

[0037] The verification calculation module 12 is configured to receive the trigger value transmitted by the trigger set module according to the read operation, per...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com