Stage structure of three-dimensional memory and formation method of stage structure

A memory and step technology, which is applied in the manufacture of electrical solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of complex process, large volume of 3D memory, high production cost of 3D memory, etc., to reduce production cost and volume Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] According to an embodiment of the present invention, a step structure in a three-dimensional memory is provided, such as figure 1 and figure 2 shown, including:

[0033] Substrate;

[0034] An array stack structure on a substrate;

[0035] The array stack structure includes multiple layers of nitride layers and oxide layers deposited alternately with a preset thickness, and the nitride layer is located between adjacent oxide layers;

[0036] A step structure with three regions and multi-layer steps is formed by performing three etching processes in the Y direction and multiple times in the X direction on the array stack structure through a mask plate.

[0037] Wherein, the substrate is preferably a silicon substrate;

[0038] It should be noted that the number of nitride layers and oxide layers in the array stack structure depends on requirements, figure 2 For example only.

[0039] According to an embodiment of the present invention, the predetermined thickness...

Embodiment 2

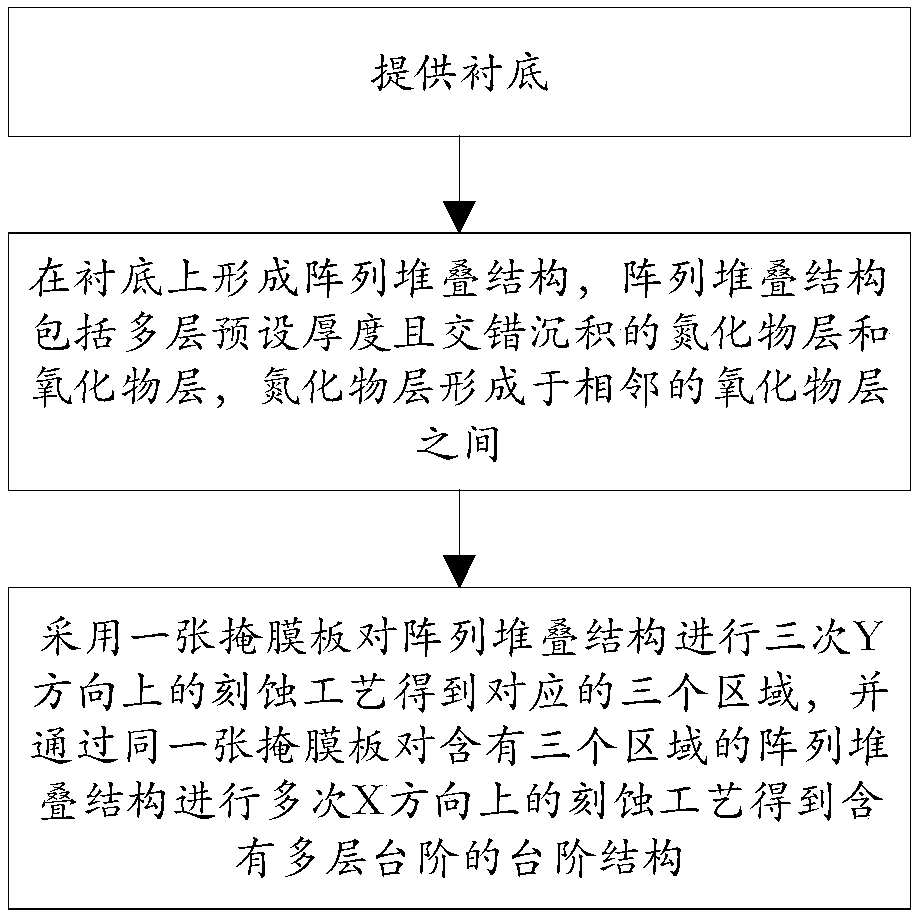

[0046] According to an embodiment of the present invention, a method for forming a step structure suitable for the three-dimensional memory described in Embodiment 1 is provided, such as image 3 shown, including:

[0047] provide the substrate;

[0048] An array stack structure is formed on the substrate, the array stack structure includes multiple layers of nitride layers and oxide layers deposited alternately with a preset thickness, and the nitride layer is formed between adjacent oxide layers;

[0049] Use a mask plate to etch the array stack structure three times in the Y direction to obtain the corresponding three regions, and perform multiple times of etching in the X direction on the array stack structure containing three regions through the same mask plate The etching process obtains a stepped structure containing multiple steps.

[0050] Wherein, the substrate is preferably a silicon substrate, and the number of nitride layers and oxide layers in the array stack s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com