Circuit structure and method for expanding number of operation times of memory

A technology of circuit structure and number of operations, applied in static memory, digital memory information, information storage, etc., can solve the problem that phase change memory cannot realize the read-write and erase balance of memory cells, and achieve the effect of avoiding excessive operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

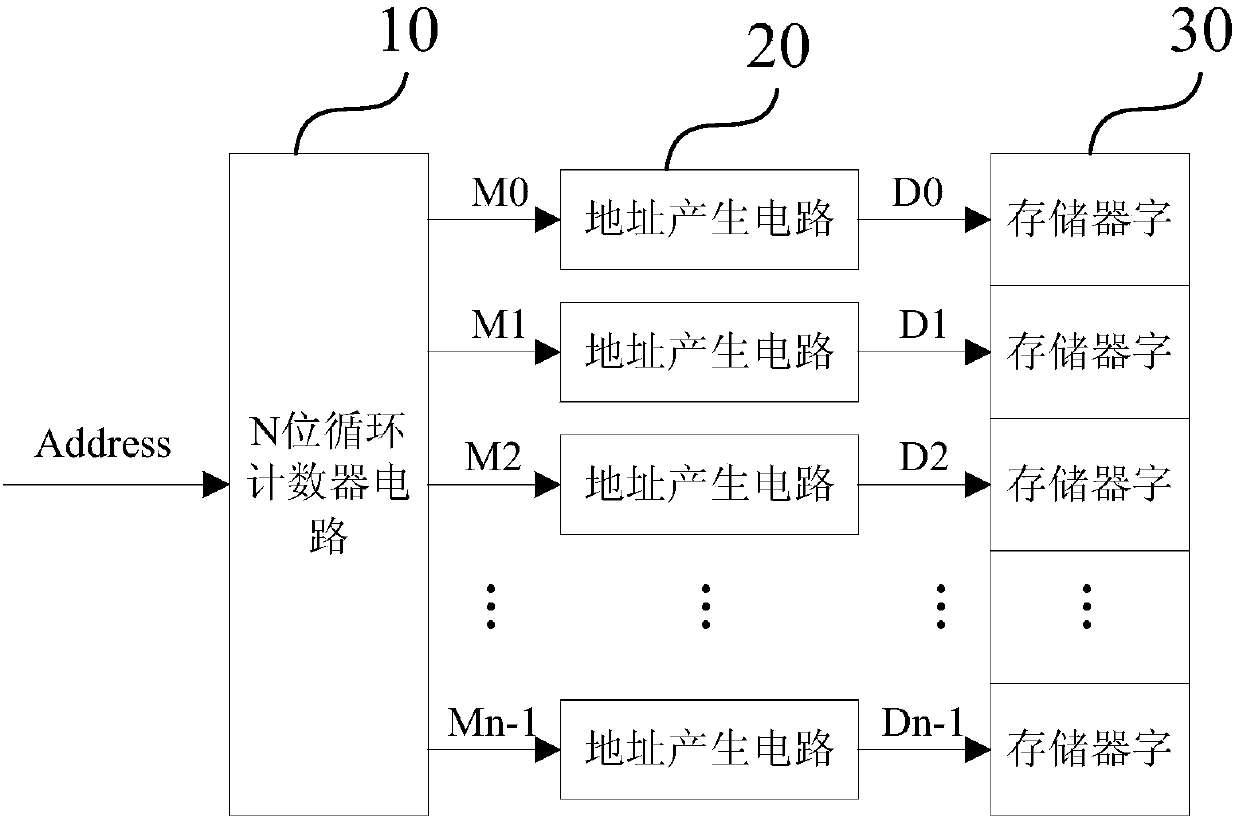

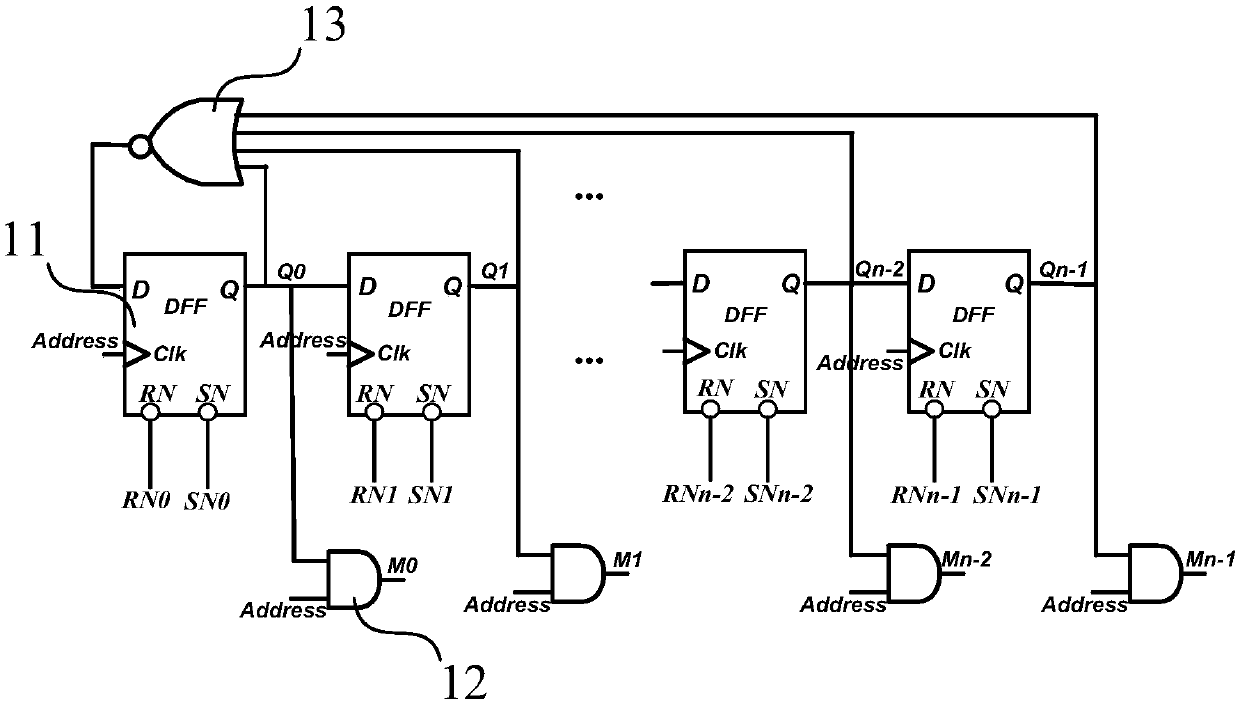

[0078] Such as figure 1 As shown, this embodiment provides a circuit structure for extending the number of memory operations, and the circuit structure includes:

[0079] The N-bit cycle counter circuit 10 is used to sequentially generate a valid output signal at N output terminals according to the input address pulse signal, and generate a set signal and a reset signal fed back by the circuit according to the address when the circuit structure is powered on , restoring the state of the N-bit loop counter circuit to the state before power-off;

[0080] N address generation circuits 20 are connected with the N-bit loop counter circuit 10, and are used to make an effective output signal generated by an output terminal of the N-bit loop counter circuit when the circuit structure is working normally, so as to be compatible with the described N-bit loop counter circuit. The address generation circuit corresponding to the output terminal generates an address signal and outputs it; ...

Embodiment 2

[0105] This embodiment provides a method for expanding the number of memory operations by using the circuit described in Embodiment 1. The method includes:

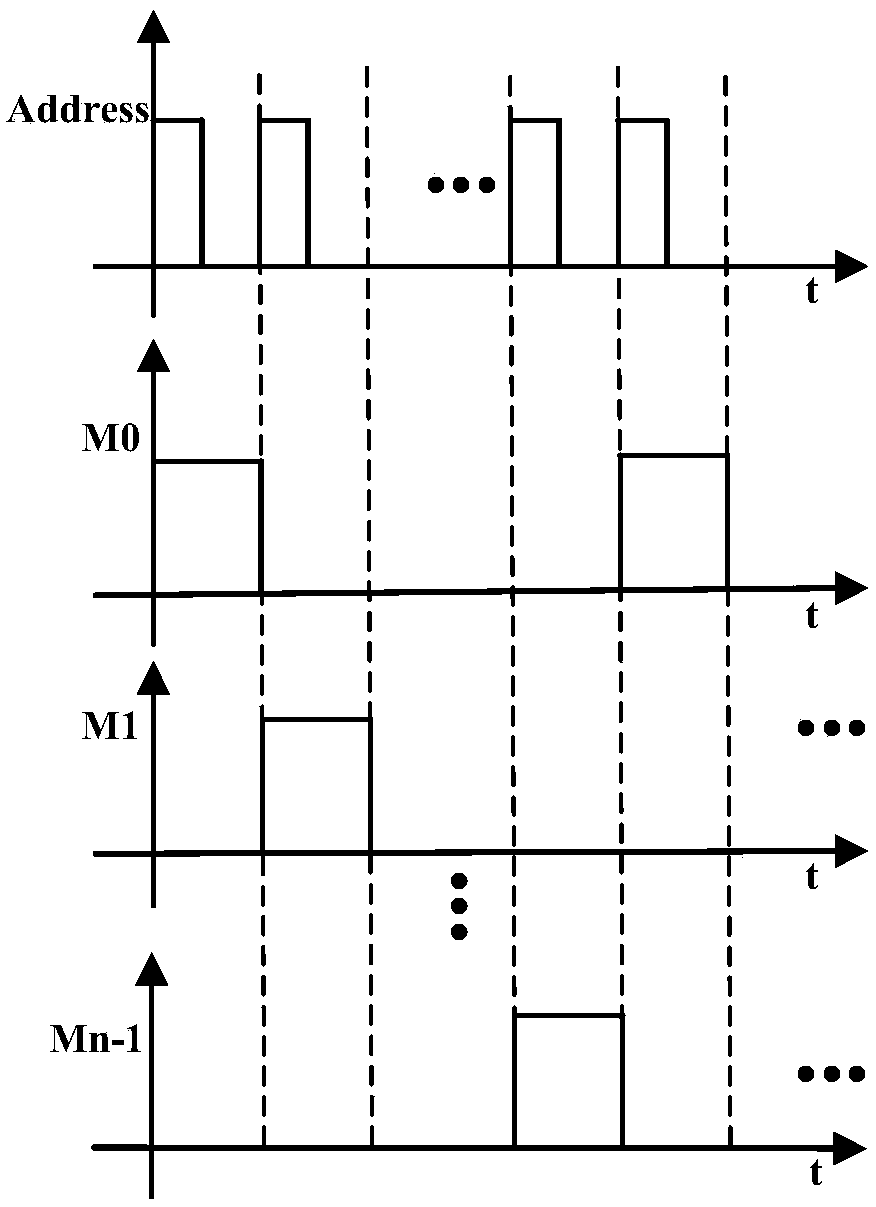

[0106] When the circuit structure is working normally, the N-bit cycle counter circuit generates an effective output signal at the N output terminals sequentially according to the input address pulse signal, and the N address generation circuits generate a valid output signal according to the N-bit cycle counter circuit An effective output signal generated by an output terminal causes the address generation circuit corresponding to the output terminal to generate an address signal and output it, and the memory array will input the address signal output by the address generation circuit to the memory array write the data into the memory word corresponding to the address signal, and realize that the input data is written in N memory words in turn;

[0107] When the circuit structure is powered off, the N address generation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com