Method for positioning failure of power device

A power device and failure location technology, which is applied in radiation pyrometry, instruments, scientific instruments, etc., can solve problems such as increased leakage current and shortened service life of devices, and achieves design cost reduction, fast response speed, and high sensitivity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Below in conjunction with accompanying drawing, specific embodiment of the present invention is described further:

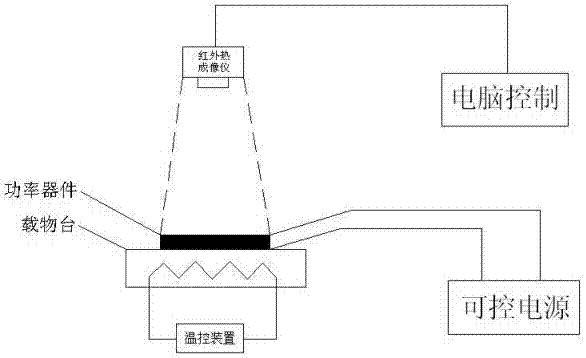

[0018] like figure 1 As shown, the equipment used in the power device failure location method described in the patent of the present invention consists of a stage with a temperature control device, an infrared thermal imager connected to a computer, and an external controllable power supply.

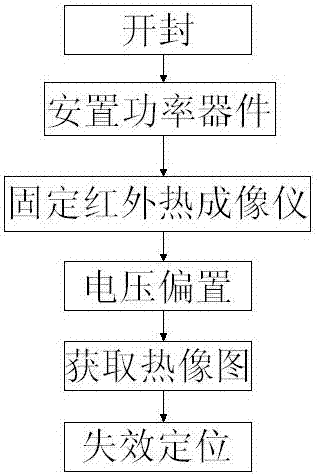

[0019] like figure 2 As shown, the patent of the present invention is a failure location method for power devices. Include the following steps:

[0020] Step 1: For power devices in non-hermetic epoxy molding compound packages, chemical corrosion is used for unsealing, while for power devices in hermetic epoxy molding compound packages or metal packages, mechanical methods are used for unsealing. The principle is not to destroy the electrical connection of the power device, and the goal is to completely expose the upper surface of the chip.

[0021] Step 2: Pla...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com