Method for measuring static quality of FPGA software

A static quality and software quality technology, applied in software testing/debugging, instrumentation, electrical digital data processing, etc., can solve problems such as unfairness and over-roughness, improve efficiency, reduce test costs, and quantify static testing quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

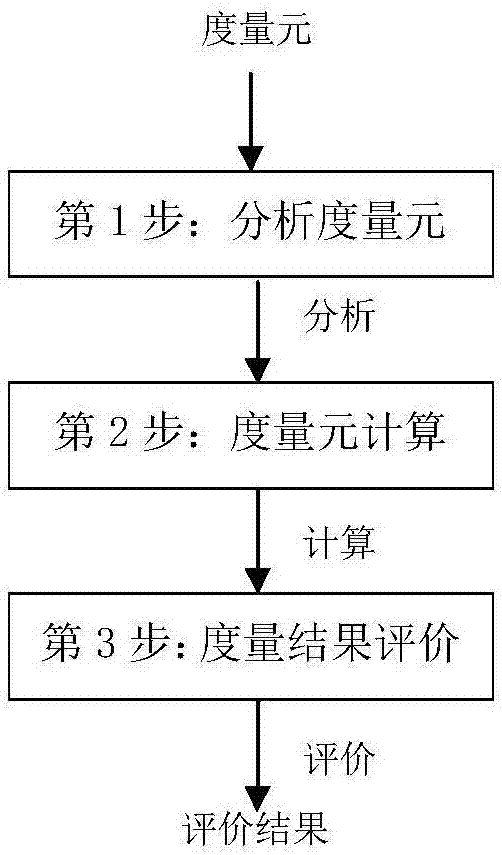

[0025] refer to figure 1 . In order to be able to objectively evaluate the quality of inspection results, the evaluation process needs to be divided into "three steps".

[0026] next figure 1 In the entire evaluation process shown, step-by-step includes three processes of analysis, calculation and evaluation. In the evaluation process, more attention is paid to the analysis and calculation of metric elements. Different from the traditional evaluation process of FPGA software quality measurement, the new process will Transform and give the final evaluation results.

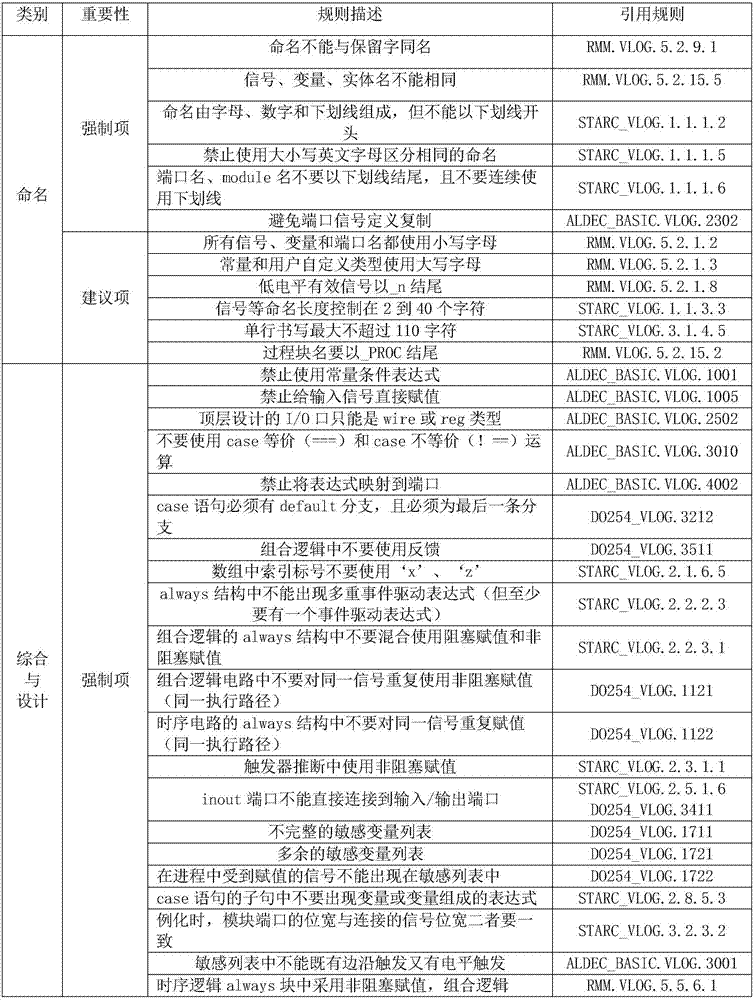

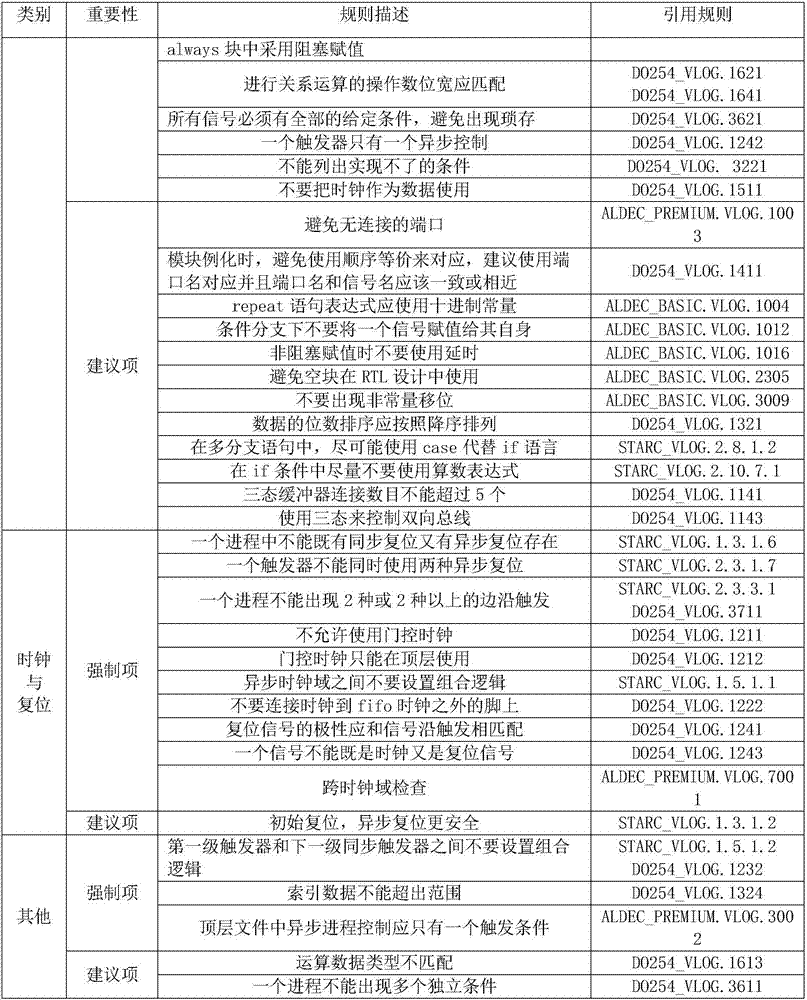

[0027] Step 1, analyze metrics: in the FPGA software including VHDL and Verilog, analyze and evaluate the types of metrics violated, filter out the metrics that reflect the value of software quality, and set the metrics and their weighting coefficients , classify and weight FPGA software metrics, and assign larger values to those that have a great impact on software code quality and are significantly different...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com