A Non-rectangular Layout Method of FPGA Reconfigurable Resources Based on Clipping Method

A layout method, non-rectangular technology, applied in the field of electronics, can solve the problems of long time-consuming layout algorithm, layout failure, etc., and achieve the effect of improving the success rate of layout, reducing the complexity of the model, and improving the calculation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

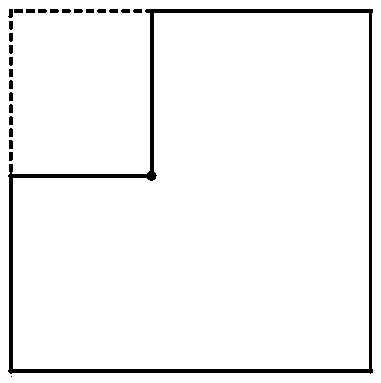

[0040] see Figure 1 to Figure 8 , the invention discloses a method for non-rectangular layout of FPGA reconfigurable resources based on clipping method, comprising the following steps:

[0041] S1, non-rectangular model modeling

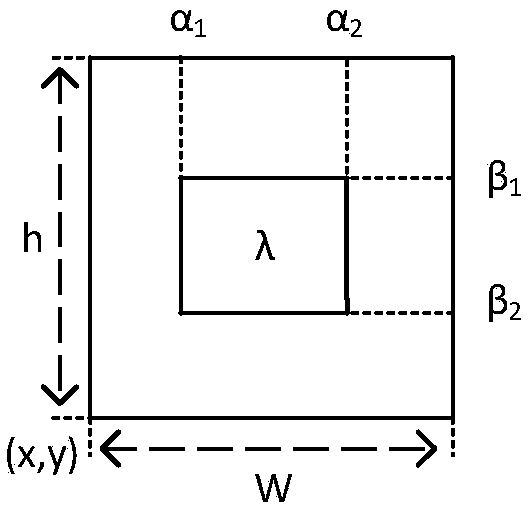

[0042] Define the set of regions to be laid out for n logic functions N={x i ,y i ,w i ,h i ,λ i},i=1,2,...,n, such as figure 1 shown by x i ,y i ,w i ,h i A rectangular logical function area to be laid out can be determined, x indicates the abscissa of the starting position of the area, y indicates the ordinate of the starting position, w indicates the width, and h indicates the height.

[0043] Among them, λ is the clipping range, λ i ={α i1 ,α i2 ,β i1 ,β i2}, α is the abscissa, and β is the ordinate.

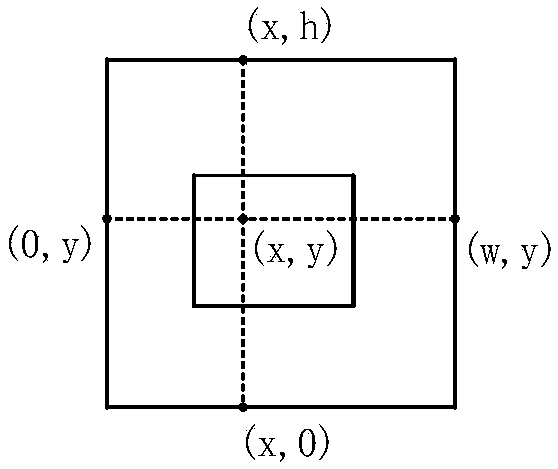

[0044] Specific clipping method: traverse all points within the λ range, and calculate the projection of each point in the horizontal (x-axis) and vertical (y-axis) directions, such as figure 2 As shown, the coordinates of the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com