Device and method for realizing automatic reading and writing test of ddr interface based on fpga

A technology of automated testing and reading and writing testing, applied in the field of data communication, can solve the problems of inaccurate test data and long test cycle, and achieve the effects of high timing accuracy, improved accuracy, fast and accurate automated testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

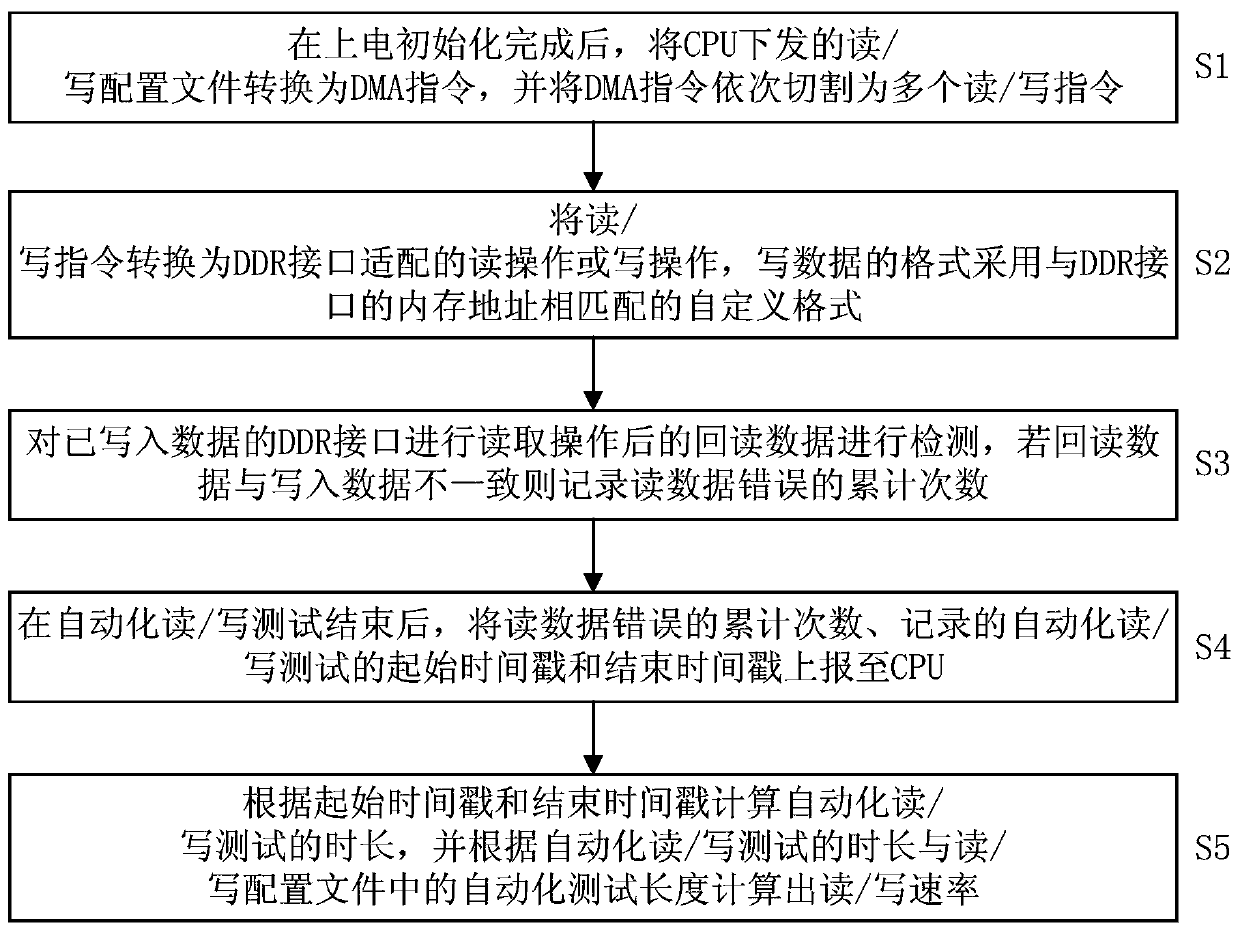

[0034] In order to solve the problem that in the existing FPGA-based DDR controller design, the mode of using CPU to execute read and write commands to test the DDR controller user interface, the test cycle is long and the test data is inaccurate, the present invention implements a DDR interface based on FPGA. The device and method for automated read-write test support users to perform batch automated read-write test operations similar to DMA (Direct Memory Access, direct memory access). Accurate automated testing enables accurate calculation of read and write rates, greatly simplifying user operations.

[0035] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

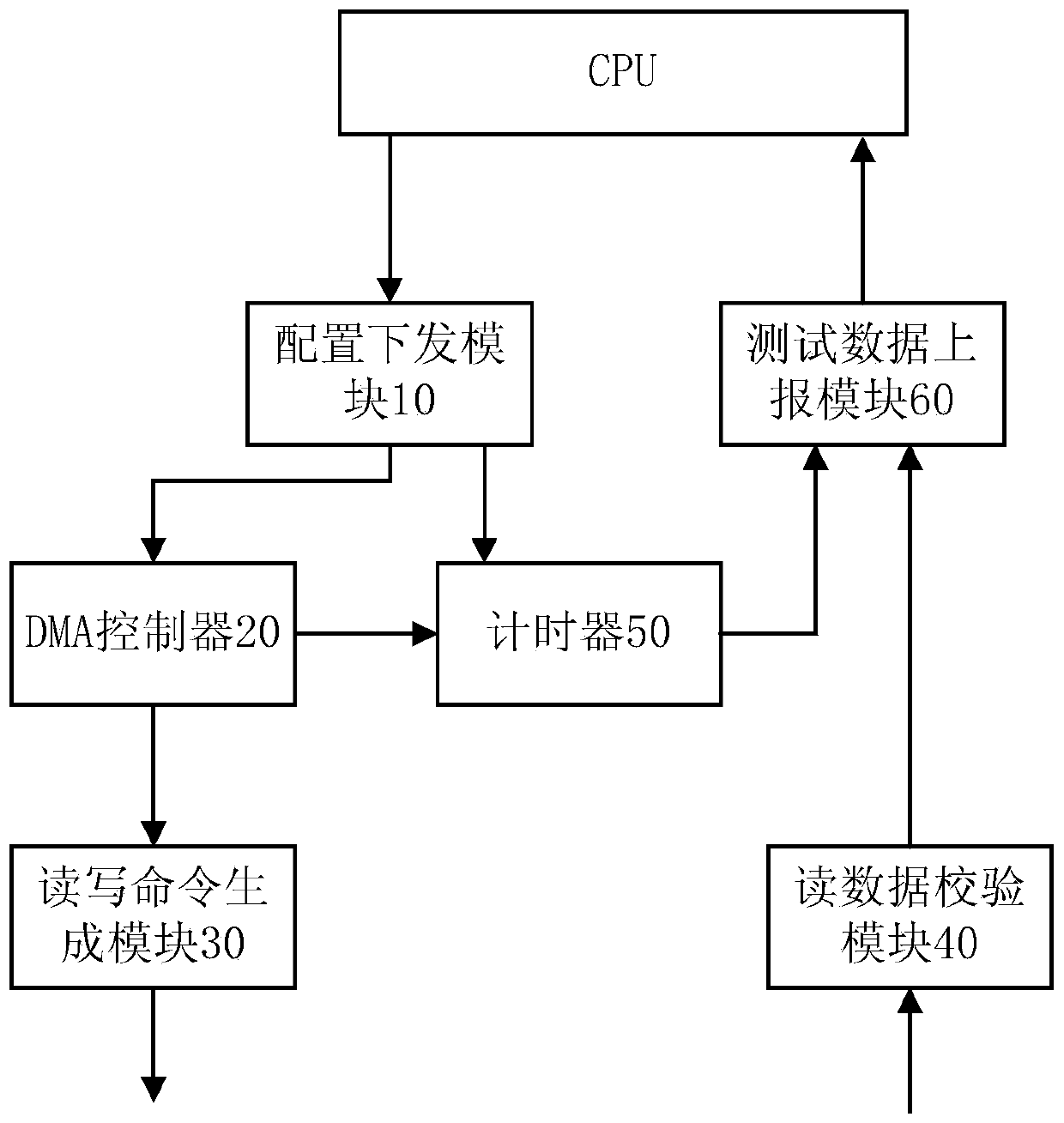

[0036] The embodiment of the present invention provides a device based on FPGA to realize automatic reading and writing test of DDR interface, such as figure 1 As shown, it includes a configuration delivery module 10 , a DMA controller 20 ,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com