FPGA (Field-Programmable Gate Array) device upgrading method and system based on Ethernet link

A technology of Ethernet and equipment, applied in the computer field, can solve the problem of inconvenient opening of the equipment shell

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

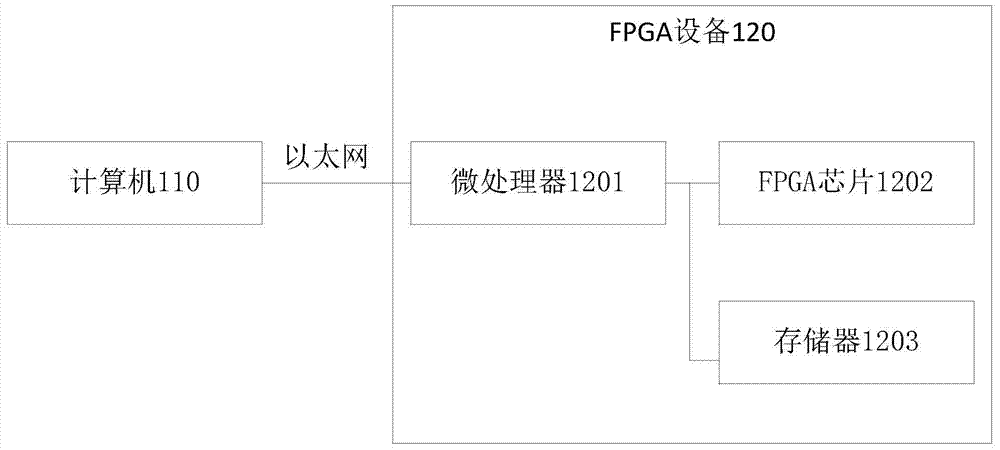

[0030] The embodiment of the present invention discloses an FPGA device upgrade system based on Ethernet link, such as figure 1 Said, the system includes: FPGA device 120 to be upgraded and computer 110, wherein:

[0031] The FPGA device 120 to be upgraded is provided with a microprocessor 1201, a memory 1203, and an FPGA chip 1202;

[0032] The computer 110 and the FPGA device are connected through an Ethernet interface, and a data frame for establishing a link is sent to the FPGA device 120 through the Ethernet interface, so that the FPGA device 120 establishes an upgrade link with the computer;

[0033] The microprocessor 1201 is connected to the memory 1203 through an SPI bus, and is configured to write the binary program file read from the computer into the memory 1203;

[0034] The FPGA chip 1202 is connected to the memory 1203 via an SPI bus, and is used to read the binary program file stored in the memory 1203 connected to it.

[0035] The upgrade system disclosed in the embodim...

Embodiment 2

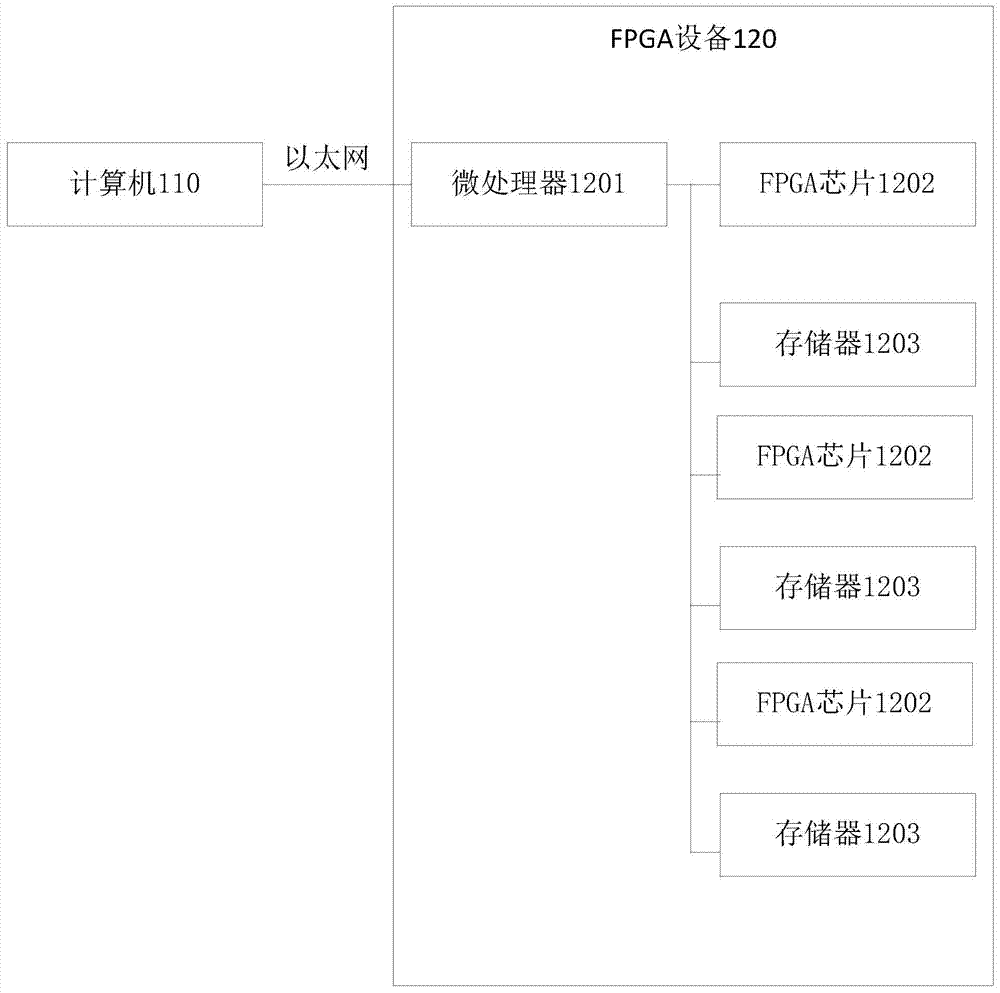

[0037] In another specific embodiment of the present invention, such as figure 2 As shown, the FPGA device 120 to be upgraded is provided with multiple FPGA chips 1202, and each of the FPGA chips 1202 is respectively connected to the microprocessor 110 through an SPI bus.

[0038] Correspondingly, during specific implementation, the FPGA device 120 to be upgraded is provided with the same number of memories 1203 as the FPGA chips 1202, and each piece of the FPGA chip 1202 is connected to a piece of memory 1203 via an SPI bus. Each piece of memory 1203 is used to store the upgrade code file of the FPGA chip 1202 connected to it.

[0039] By configuring a piece of memory for each FPGA chip, parallel upgrades can be realized and the efficiency of FPGA device upgrades can be improved.

Embodiment 3

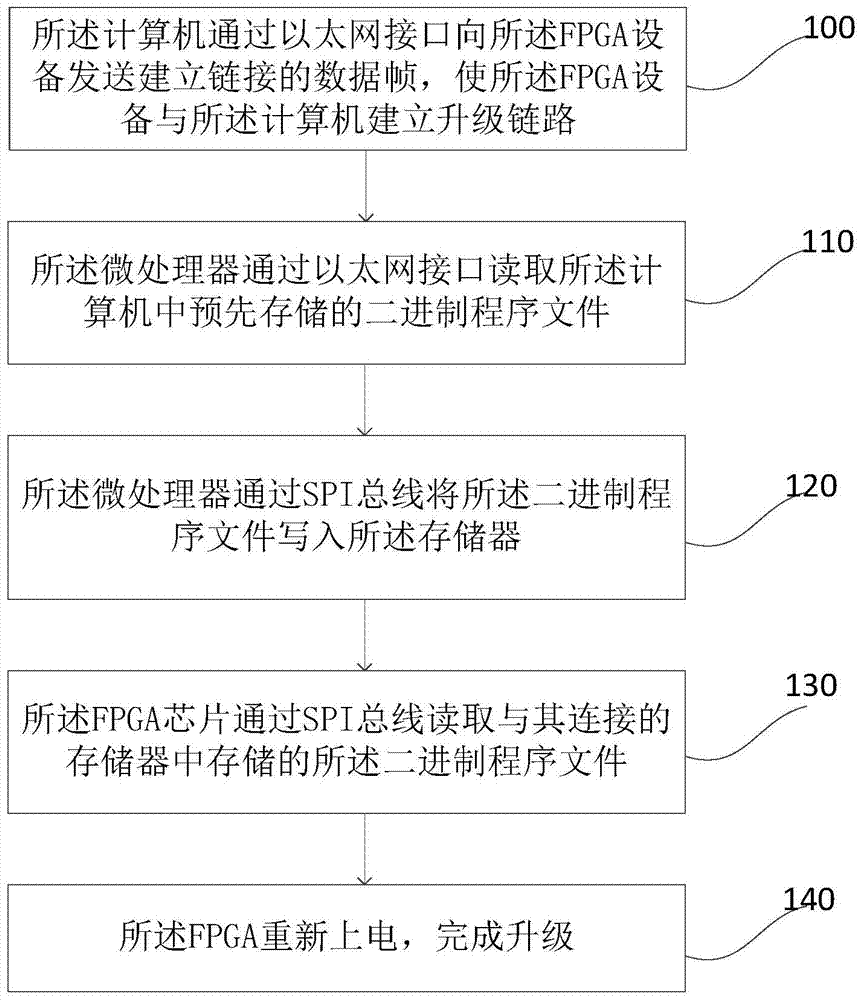

[0041] Correspondingly, the embodiment of the present invention also discloses a method for upgrading an FPGA device based on an Ethernet link, which is applied to the FPGA device upgrade system based on an Ethernet link disclosed in the first and second embodiments. Such as image 3 As shown, the upgrade method includes:

[0042] Step 100: The computer sends a data frame for establishing a link to the FPGA device through an Ethernet interface, so that the FPGA device and the computer establish an upgrade link;

[0043] Step 110: The microprocessor reads the binary program file pre-stored in the computer through the Ethernet interface;

[0044] Step 120: The microprocessor writes the binary program file into the memory via the SPI bus;

[0045] Step 130: The FPGA chip reads the binary program file stored in the memory connected to the FPGA chip through the SPI bus;

[0046] Step 140: The FPGA is powered on again to complete the upgrade.

[0047] The upgrade method disclosed in the embod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com