Image sensor chip packaging structure and packaging method

An image sensor and packaging method technology, which is applied to semiconductor devices, electric solid state devices, radiation control devices, etc., can solve the problems of complex packaging structure, difficult packaging process of wafer-level image sensors, and complex through-silicon via interconnection process, etc. To achieve the effect of simplifying the packaging structure and process, avoiding poor connection reliability and avoiding poor reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

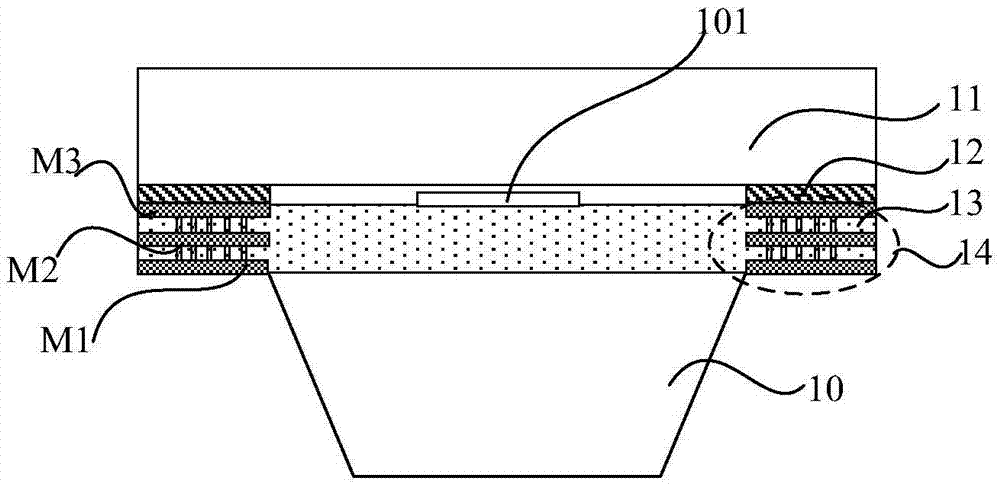

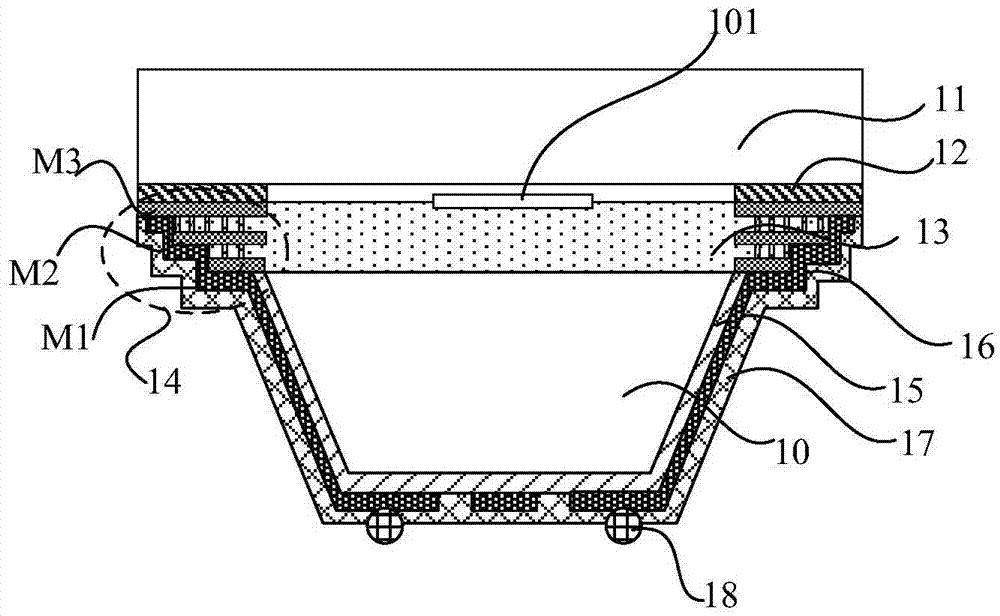

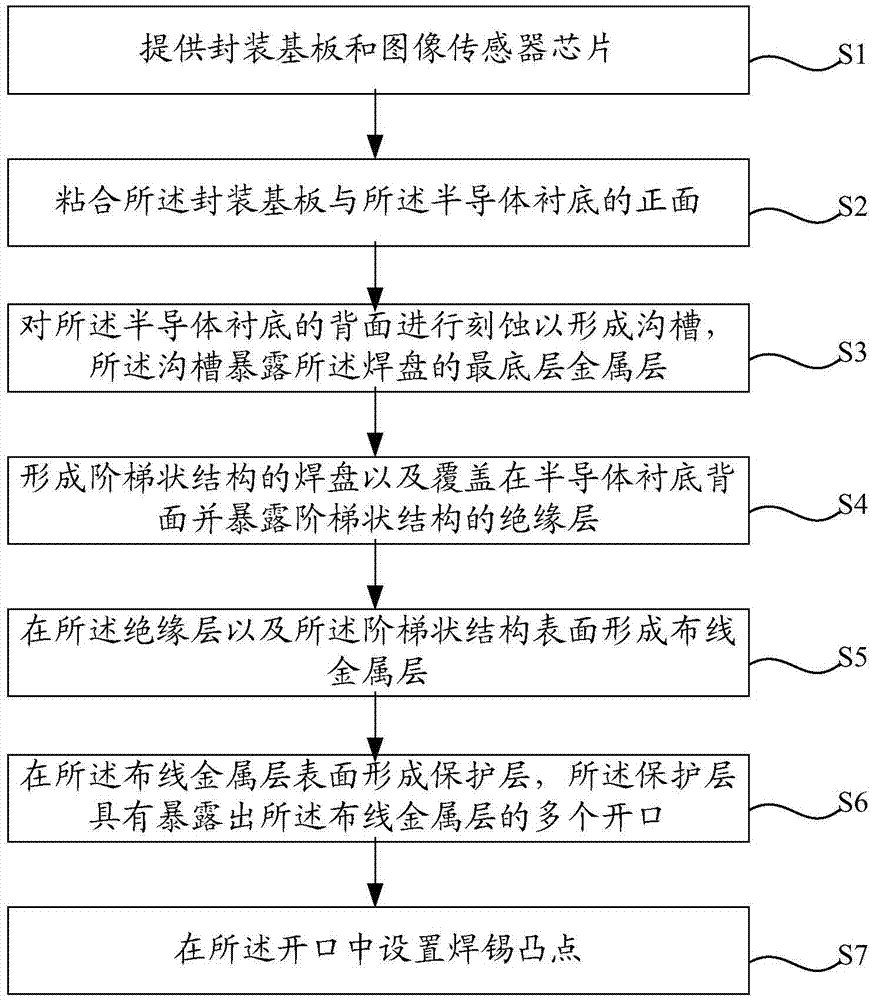

[0047] The core idea of the present invention is to provide a non-through-silicon via, low-cost image sensor flip packaging process, which uses the substrate trench etching process on the back of the chip to avoid the use of the through-silicon via (TSV) process, and at the same time exposes the bottom of the trench The outer peripheral edge of the pad is modified into a stepped structure, thereby reducing the difficulty of filling the wiring metal layer, increasing the contact area between the subsequent filled wiring metal layer and the pad, and improving the connection reliability of the wiring metal layer.

[0048]In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

[0049...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com