Fixed-point multiplying accumulator

A multiplication accumulator, fixed-point technology, applied in the field of fixed-point multiplication accumulator, can solve the problems of increasing the length of the critical path, performance degradation, etc., and achieve the effect of realizing the multiplication/accumulation/subtraction function, increasing the delay, and ensuring performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] Embodiment 1. Fixed-point integer / decimal multiplication function:

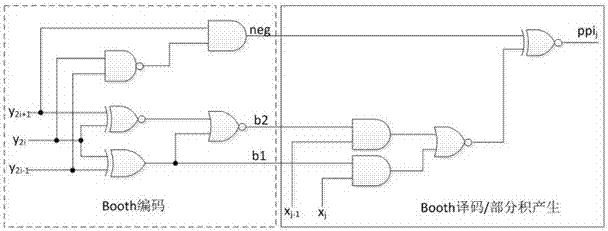

[0041] This embodiment proposes a multiply-accumulator, which mainly includes a Booth coding unit, a left-shift logic unit, a Booth decoding / partial product generating unit, a compression tree, a compressor, an accumulator, an adder, etc., see figure 1 As shown, both fixed-point integer multiplication and fixed-point decimal multiplication can be realized without increasing the delay of multiply-accumulator.

[0042] The Booth encoding unit is used to perform Booth encoding on the multiplier.

[0043] Booth coding is used to reduce the number of partial products, and Booth coding with radix 4 can reduce the number of partial products by half. The following table is the encoding table of base 4Booth encoding:

[0044]

[0045] where X represents the multiplicand, x i Represents the bit with the multiplicand weight i, Y represents the multiplier, y 2t-1 Represents the bit weighted 2i-1 in the multip...

Embodiment 2

[0058] Embodiment 2. Multiply-accumulate / subtract function:

[0059] This embodiment proposes a multiply-accumulator, which mainly includes a Booth encoding unit, a Booth decoding / partial product generating unit, a compression tree, a compressor, an accumulator, an adder, etc., see Image 6 As shown, both the multiply-accumulate function and the multiply-accumulate-subtract function can be realized without increasing the delay of the multiply-accumulator.

[0060] The difference between the Booth coding unit in this embodiment and the first embodiment is that when performing a multiply-accumulate-subtract operation, the Booth coding unit performs Booth coding on the multiplier and then inverts the coding value neg to obtain a new Booth coding value neg_new; then use neg_new produces partial products, see Figure 7 shown.

[0061] Because the critical path of Booth encoding and decoding is the path where the encoded value b1 / b2 is located, the generation of Neg_new does not a...

Embodiment 3

[0072] Embodiment 3. Overflow judgment function:

[0073] In the prior art decimal multiplication, when two -1s are multiplied, saturation selection processing (overflow processing) is performed after the multiplication result is obtained, which has the disadvantage of increasing the length of the critical path.

[0074] In view of the above problem, if the multiply-accumulator needs to automatically saturate the multiplication result before accumulation, add operand judgment logic, and overflow only when both operands are -1. Therefore, this embodiment proposes a Multiply accumulator, mainly including Booth coding unit, Booth decoding / partial product generation unit, overflow judgment unit 1001, compression tree, compressor, accumulator, adder, etc., see Figure 9 As shown, the multiply-accumulate function and overflow judgment function are realized without increasing the length of the critical path.

[0075]The overflow judging unit 1001 is used to judge whether the multipl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com