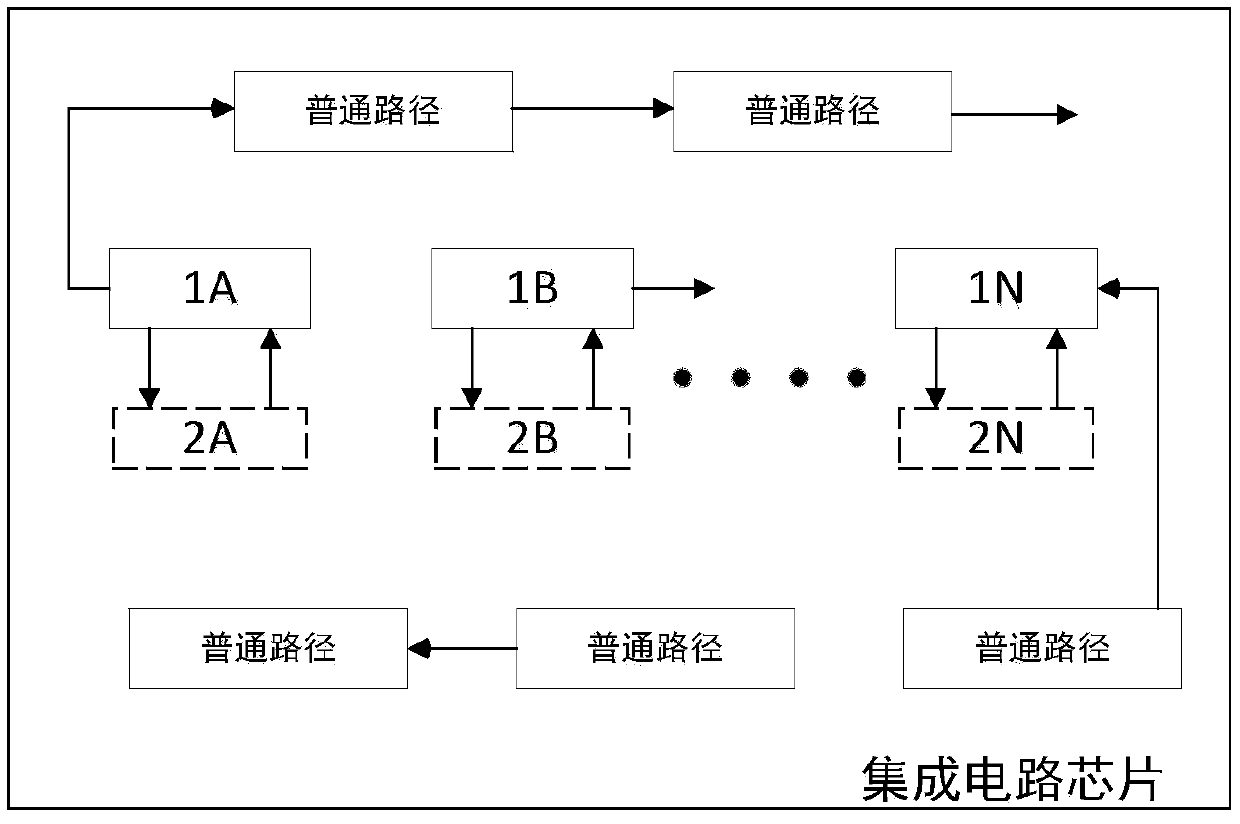

A speed hierarchical optimization structure and method for improving the output of high-performance integrated circuits

A speed grading and integrated circuit technology, applied in electrical digital data processing, instruments, calculations, etc., can solve problems such as the inconsistency of the maximum operating speed of integrated circuits, and achieve the effect of increasing profits, increasing overall profits, and increasing proportions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0100] Use the speed grading optimization structure inside the integrated circuit chip designed in the present invention to test:

[0101] The internal speed grading optimization structure of the integrated circuit chip proposed by the present invention is inserted into several test circuits, such as the FGU (Floating Point and Graphic Unit) module in the OpenSPARCT2 processor, ITC'99 The largest circuit b19, and s953, s9234, s13207, s38417, and s35932 in the ISCAS'89 test circuit. The above-mentioned circuits inserted into the on-chip adjustment structure have been simulated and verified and verified on Altera's 28nm FPGA.

[0102] First test the single path speed grading optimization structure. A path is extracted in the b19 circuit, and the delay of this path is 851ps. The extraction method is: first use Synopsys’ Design Compiler software to synthesize the b19 test circuit, add timing constraints, convert the RTL-level code into a gate-level netlist (netlist), and generate a t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com