Opportunity multithreading in a multithreaded processor with instruction chaining capability

An instruction and thread technology, applied in the field of multi-thread processing of microprocessors, can solve problems such as performance degradation, instruction memory cannot be shared by hardware threads, and memory resources are not fully utilized.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

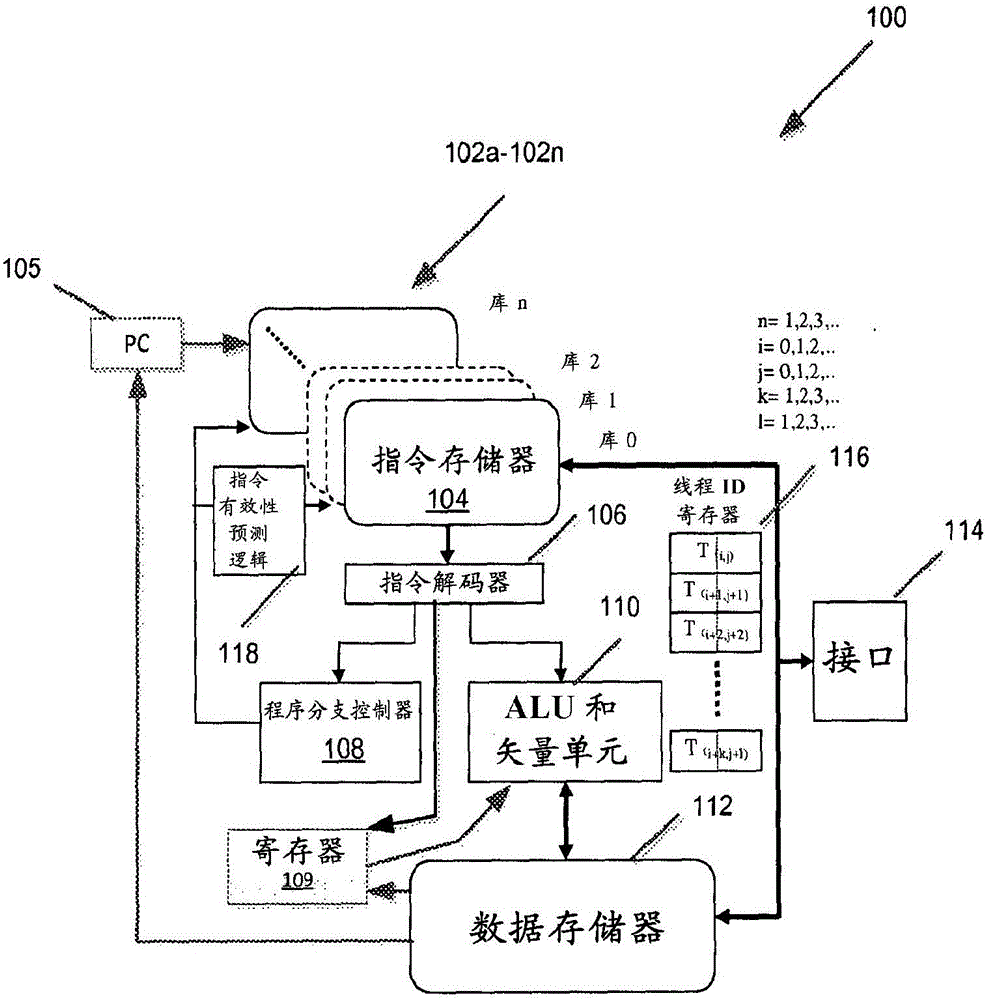

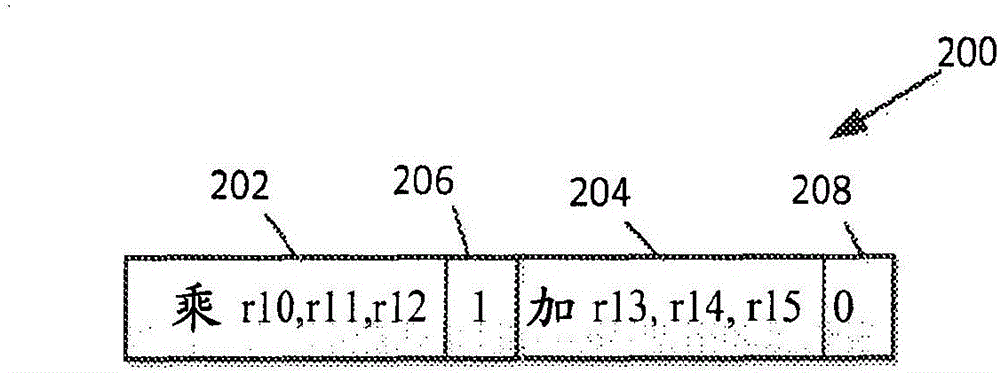

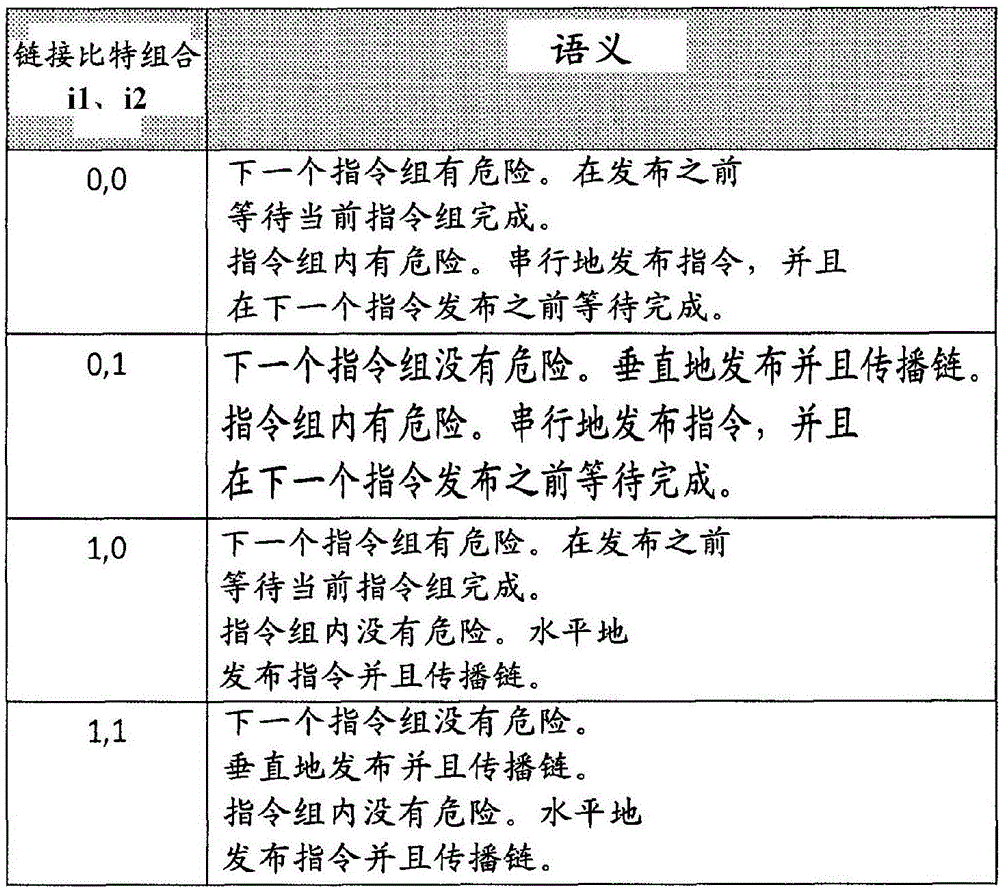

[0036] Examples of the present disclosure describe a multithreaded computer processor and method of operating the multithreaded computer processor that minimizes unused clocks in the multithreaded processor when there are fewer software threads than hardware thread units cycle. Unused clock cycles may occur when an allocated hardware thread unit must issue a NOP. Examples of the present disclosure provide methods and multithreading that can issue awaited instructions to multiple hardware thread units without requiring all preceding hardware thread units to issue NOPs first as in the case of token-triggered multithreading computer processor. An approach known as "opportunistic multithreading" controls instruction issue sequences by providing a two-dimensional array of identification registers associating software threads with several hardware thread units. In each pipeline stage, a thread identifier (ID) may be used to identify the software thread from which the instruction w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com