A Method for Obtaining Parasitic Capacitance Models Around the Gate of 3D MOS Devices

A MOS device and parasitic capacitance technology, which is applied in the field of accurate model acquisition of the parasitic capacitance around the gate of a three-dimensional MOS device, can solve problems such as slow calculation speed, difficulty in establishing capacitance models, and inability to obtain accurate continuous capacitance models, and achieves fewer fitting parameters. , the effect of wide applicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail in conjunction with the following specific embodiments and accompanying drawings. The process, conditions, experimental methods, etc. for implementing the present invention, except for the content specifically mentioned below, are common knowledge and common knowledge in this field, and the present invention has no special limitation content.

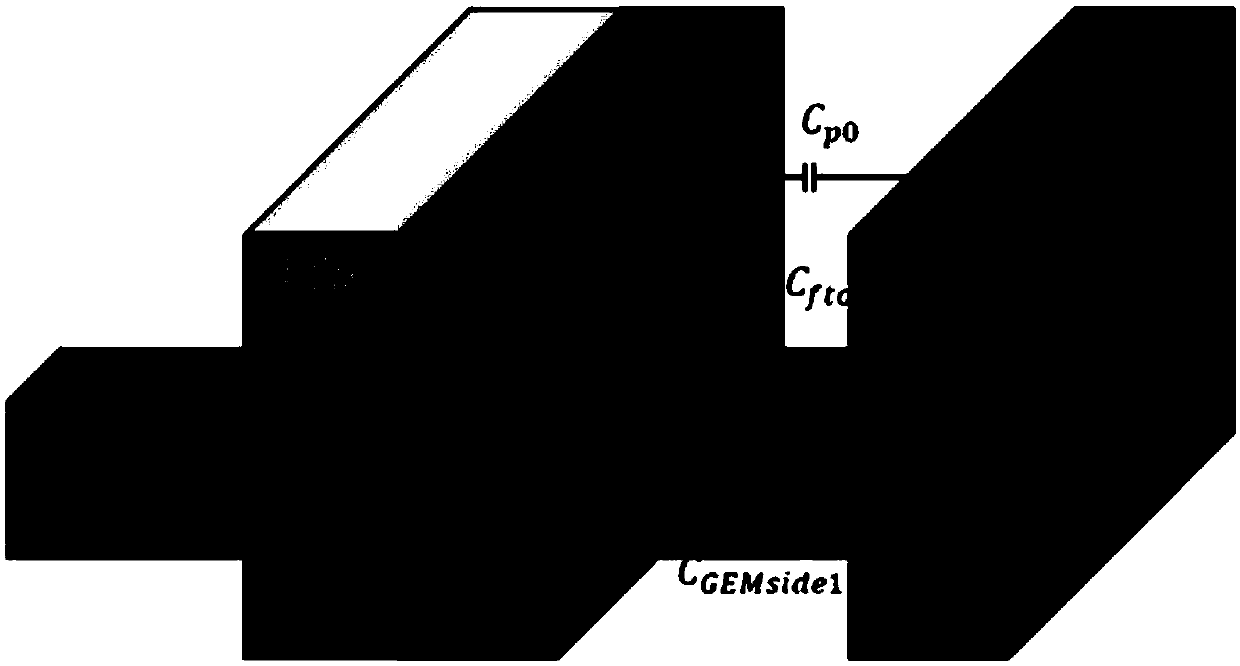

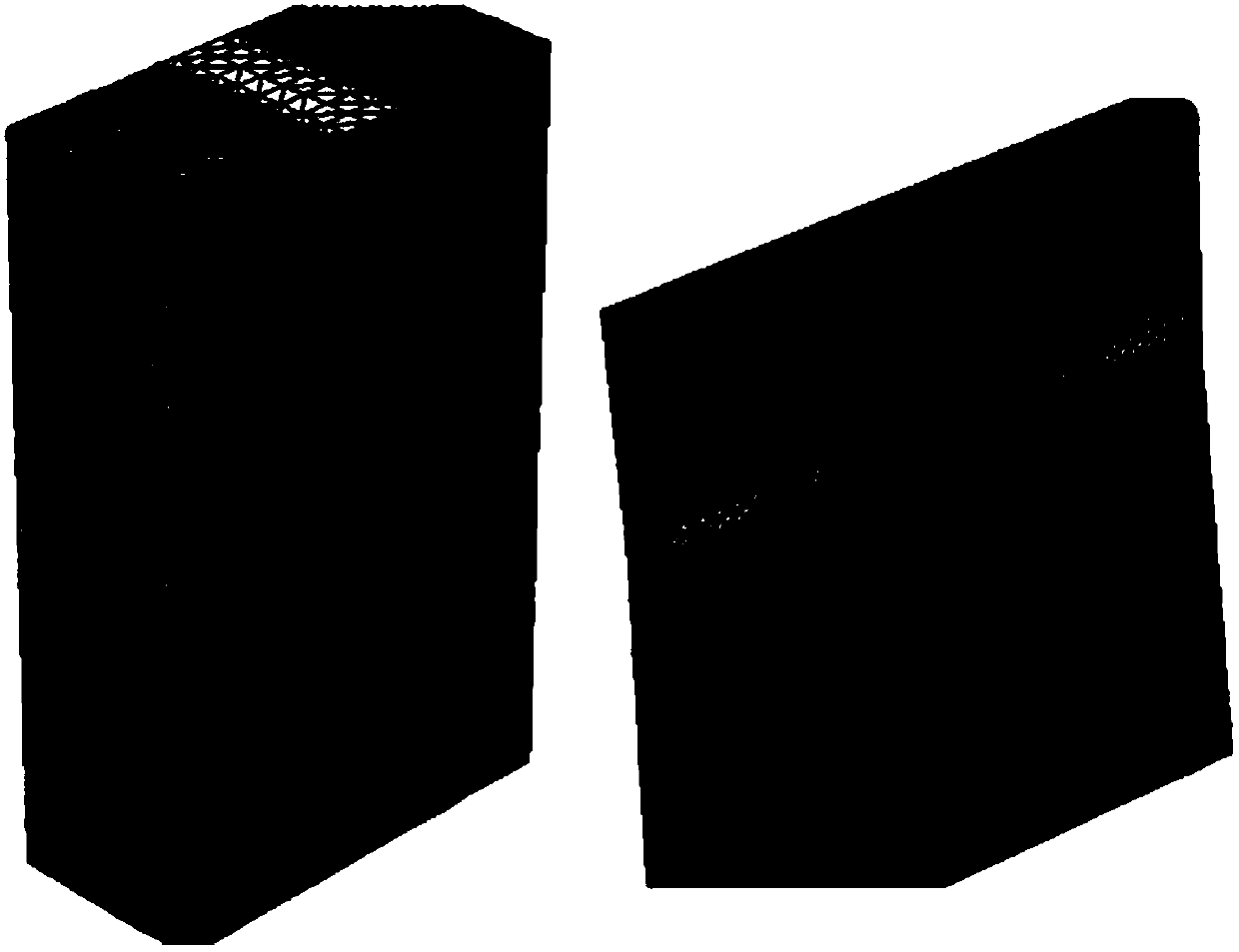

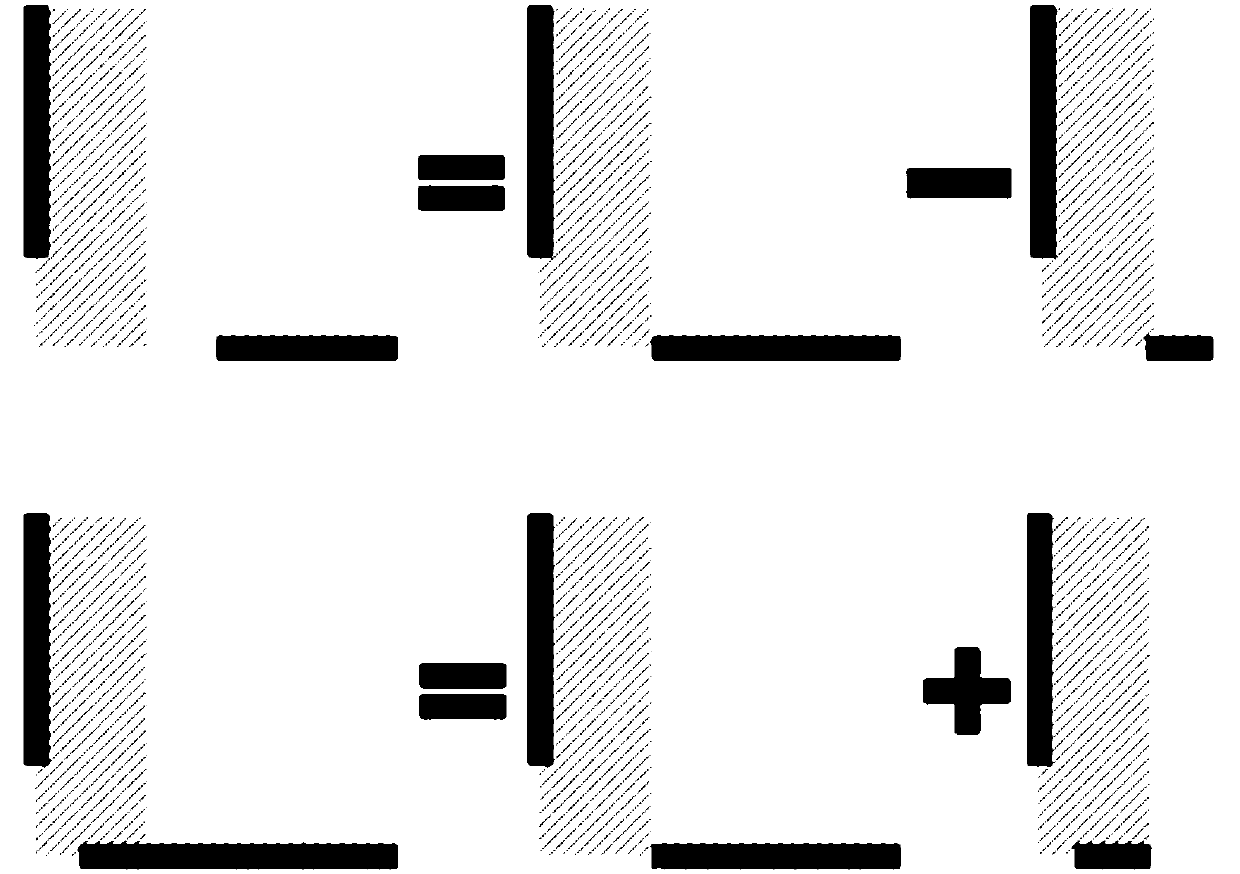

[0042] The parasitic capacitance model around the gate of the three-dimensional MOS device provided by the invention is based on the conformal transformation and can solve the situation of including multiple dielectric layers. The modeling process of the present invention includes the following steps:

[0043] Step 1: Method for dividing the parasitic capacitance around the gate of the three-dimensional MOS device. The reference basic parameters of the three-dimensional MOS device in the present invention are shown in Table 1.

[0044] Table 1: Basic parameters of three-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com