Neutral-point voltage balance and common-mode voltage suppression method for three-level inverter

A three-level inverter and voltage balancing technology, which is applied to electrical components, output power conversion devices, and AC power input to DC power output. It can solve the problems of output waveform influence and less consideration of midpoint voltage. Achieve the effect of simple logical judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

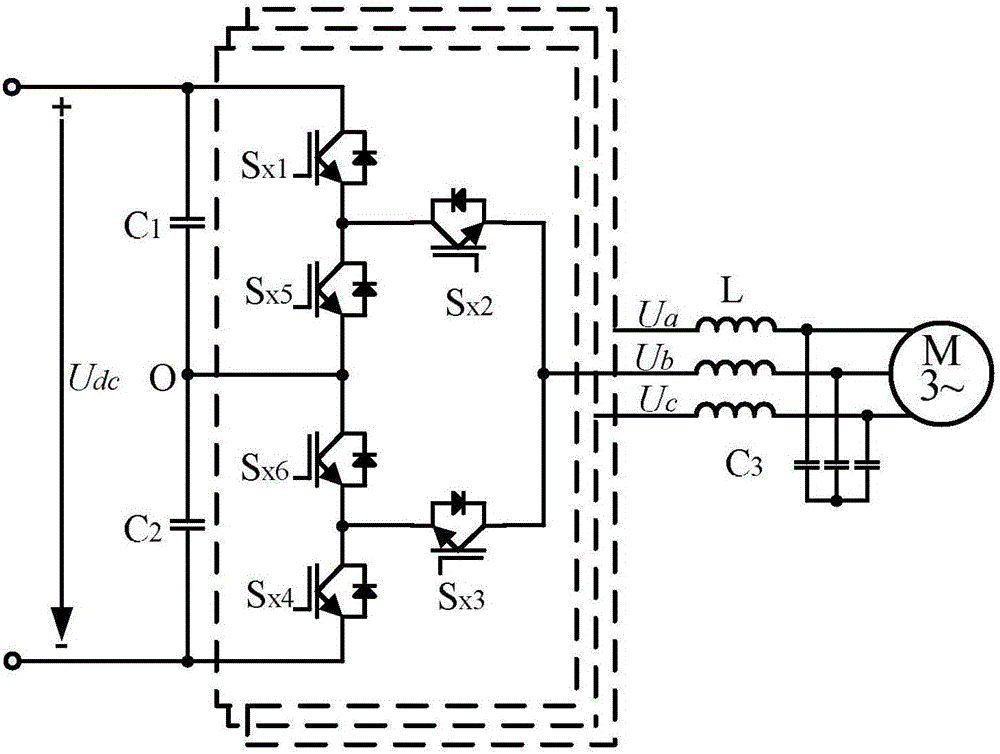

[0037] figure 1 It is a three-phase three-level ANPC inverter topology: each phase bridge arm consists of six switching devices S x1 , S x2 , S x3 , S x4 , S x5 , S x6 (where x represents the three phases of a, b, and c); C1 and C2 are the upper and lower capacitors;

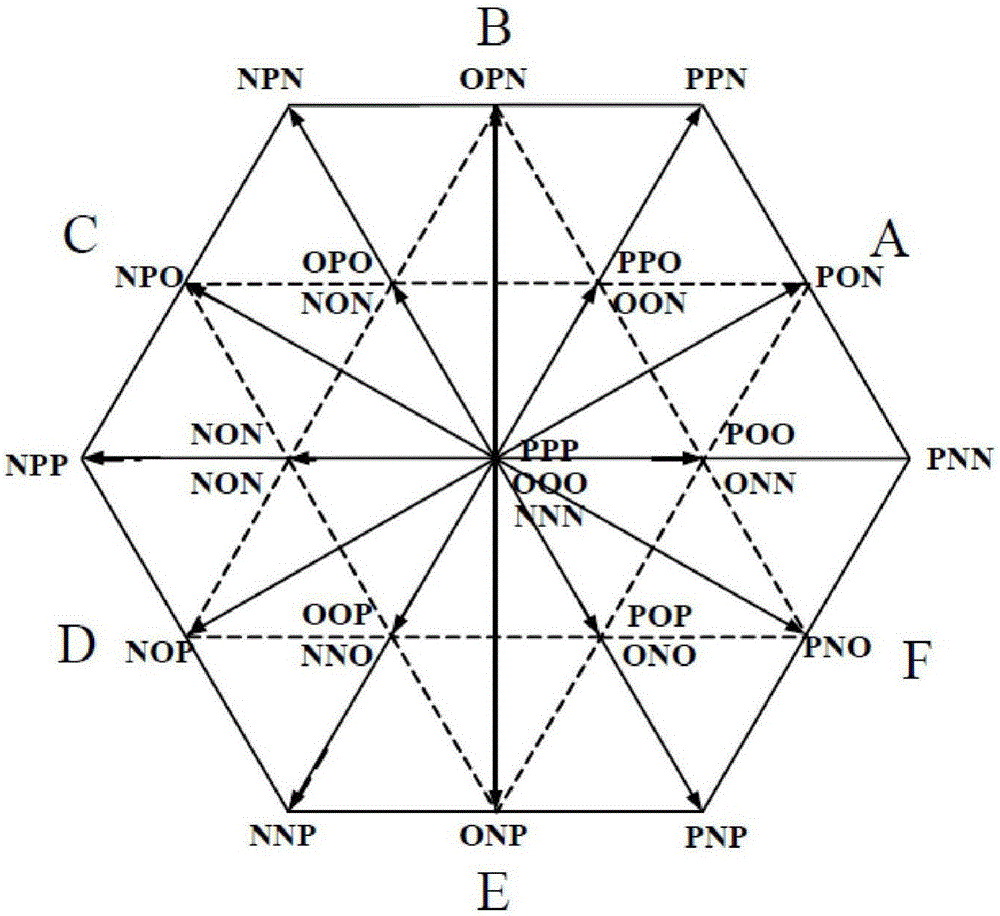

[0038] figure 2 It is a traditional three-level space vector diagram (Space Vector Diagram, SVD). The entire space vector diagram is divided into six regions A to F, and each region is similar in nature. The basic vectors of the three-level inverter can be divided into 6 large vectors, 6 medium vectors, 6 pairs of positive and negative small vectors and 3 zero vectors according to the modulus length.

[0039] Through analysis, the relationship between the three-level vector state and the common-mode voltage amplitude can be obtained as shown in the following table:

[0040] Table 1 Three-level vector state and common-mode voltage amplitude table

[0041]

[0042] It can be seen from the above table ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com