LED chip and preparation method thereof

A LED chip, N-type technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of difficulty in preparing TiW/TiWN structure, difficulty in controlling the stress of TiW single-layer structure, difficulty in TiW/Pt, etc., to ensure light output Efficiency and service life, mature etching process, effect of stress control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0022] This embodiment adopts the following steps:

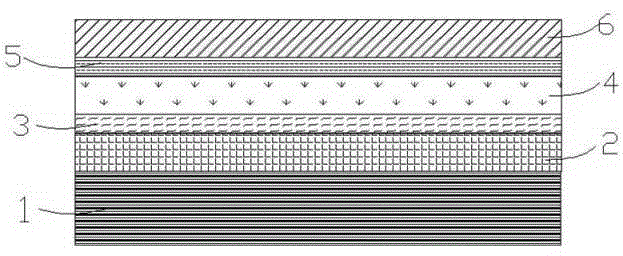

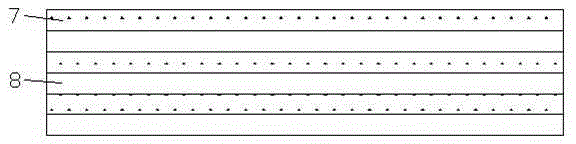

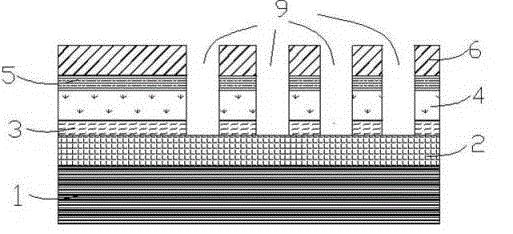

[0023] Such as figure 1 As shown, the MOCVD epitaxial growth technology is used to sequentially grow the N-type GaN layer 2, the active layer 3, and the P-type GaN layer 4 on the sapphire substrate 1; use the evaporation method to deposit Ag on the surface of the P-type GaN layer 4 as Ohmic contact and metal reflective layer 5; on the metal reflective layer 5, a protective metal layer 6 is evaporated, and the structure of the protective metal layer is as follows figure 2 shown; as image 3 As shown, the ICP dry etching method is used to etch a part of the surface of the metal reflective layer until the N-type GaN is exposed to form an N-type electrode hole 9; Figure 4 As shown, SiO was deposited by PECVD 2 passivation layer 10; evaporation of P electrode 11 and N electrode 12; finally, cutting and separating the chip to obtain a single LED chip.

Embodiment 2

[0025] This embodiment adopts the following steps:

[0026] The difference between this embodiment and the LED chip preparation method provided in Embodiment 1 is that Ag is deposited on the surface of the P-type GaN layer 4 as an ohmic contact and the metal reflective layer 5, and then the metal reflective layer 5 is etched, as shown in FIG. Figure 5 As shown, the etching stops until the surface of the P-type GaN layer 4; then a metal protective layer 6 is deposited on the etched Ag layer and the surface of the P-type GaN; as Figure 6 As shown, the etching on the surface of the protective metal layer along the edge of the etching of the reflective metal layer 5 stops at the surface of the N-type GaN, so that the side of the metal reflective layer 5 is covered by the protective metal layer 6 .

Embodiment 3

[0028] This embodiment adopts the following steps:

[0029] The difference between this embodiment and the LED chip preparation method provided in Embodiment 1 is that, after depositing Ag on the surface of the P-type GaN layer 4 as an ohmic contact and the metal reflective layer 5, the metal reflective layer 5 is etched, such as Figure 7 As shown, the etching stops until the surface of the P-type GaN layer 4; then a metal protective layer 6 is deposited on the etched Ag layer and the surface of the P-type GaN; as Figure 8 As shown, the protective metal layer 6 is etched using the ICP etching method, and the etched area is slightly smaller than the etched metal reflective layer Ag, so that the side of the metal reflective layer Ag covers the protective metal layer 6; as Figure 9 As shown, the P-type GaN layer and the active layer are etched again to form N-type electrode holes, and the N-type electrode holes are smaller than the holes etched out of the metal layer 6 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com