Time sequence correction method and electronic device

An electronic device and timing technology, applied in the fields of electrical digital data processing, CAD circuit design, special data processing applications, etc., can solve the problems of prolonging the chip design cycle, increasing the chip design cost, and increasing the chip power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] What is described in this chapter is the best way to implement the present invention. The purpose is to illustrate the spirit of the present invention rather than to limit the protection scope of the present invention. The protection scope of the present invention should be defined by the claims.

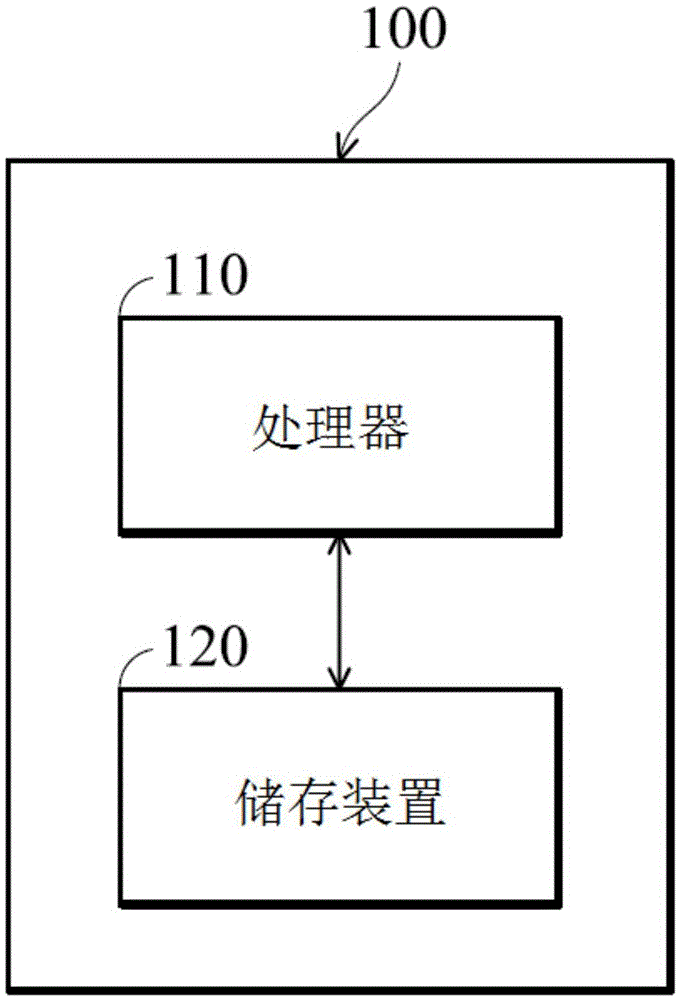

[0024] figure 1 It is a block diagram showing the electronic device 100 according to an embodiment of the present invention. The electronic device 100 is suitable for Electronic Design Automation (EDA) tools and simulation tools for integrated circuit design. The electronic device 100 can simulate circuit operation through electronic design automation (EDA) tools. Such as figure 1 As shown, the electronic device 100 includes a processor 110 and a storage device 120 . exist figure 1 The block diagram in the figure is only for the convenience of describing the embodiment of the present invention, but the present invention is not limited thereto.

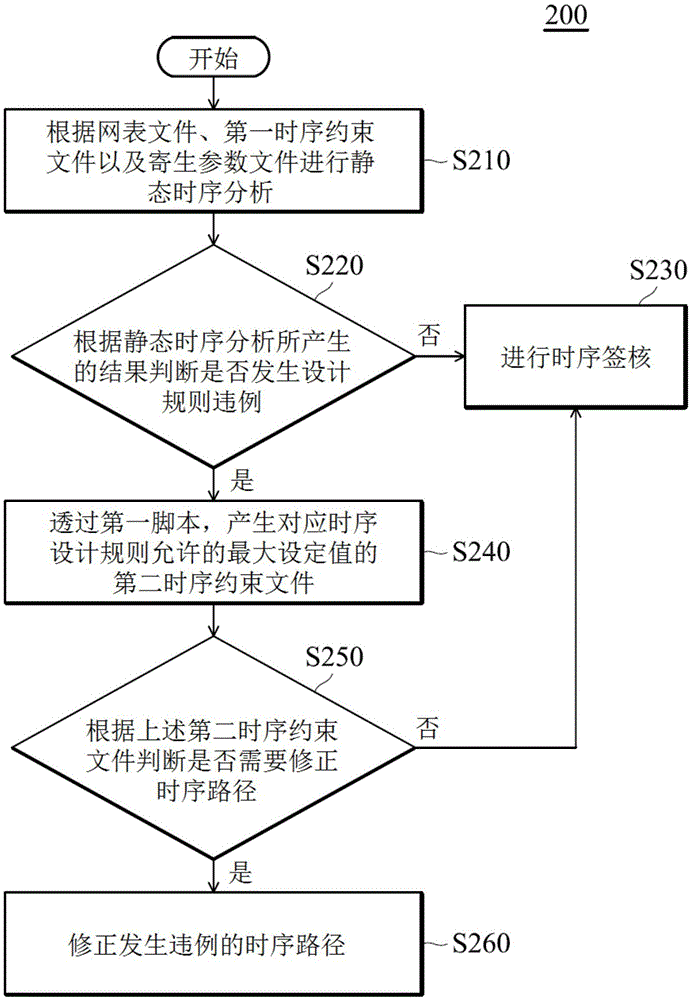

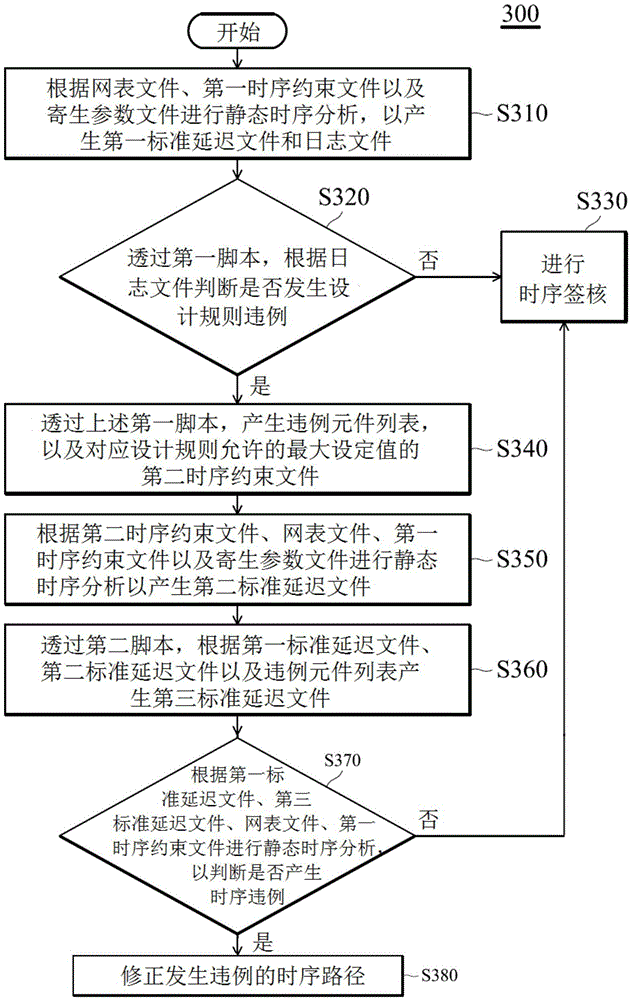

[0025] According to an em...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com