Physical unclonable chip circuit

A circuit and chip technology, applied in the field of information security, can solve the problems of high power consumption, large area overhead, and restrictions on the application of PUF chips, and achieve the effect of low power consumption and reduced area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

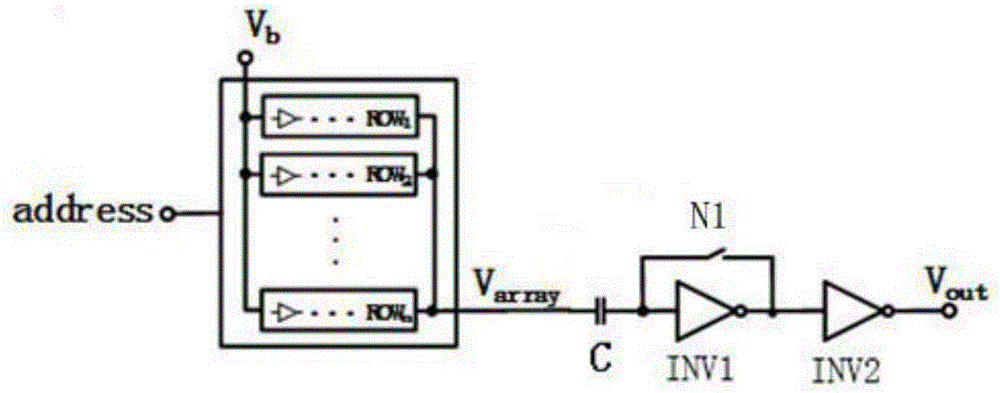

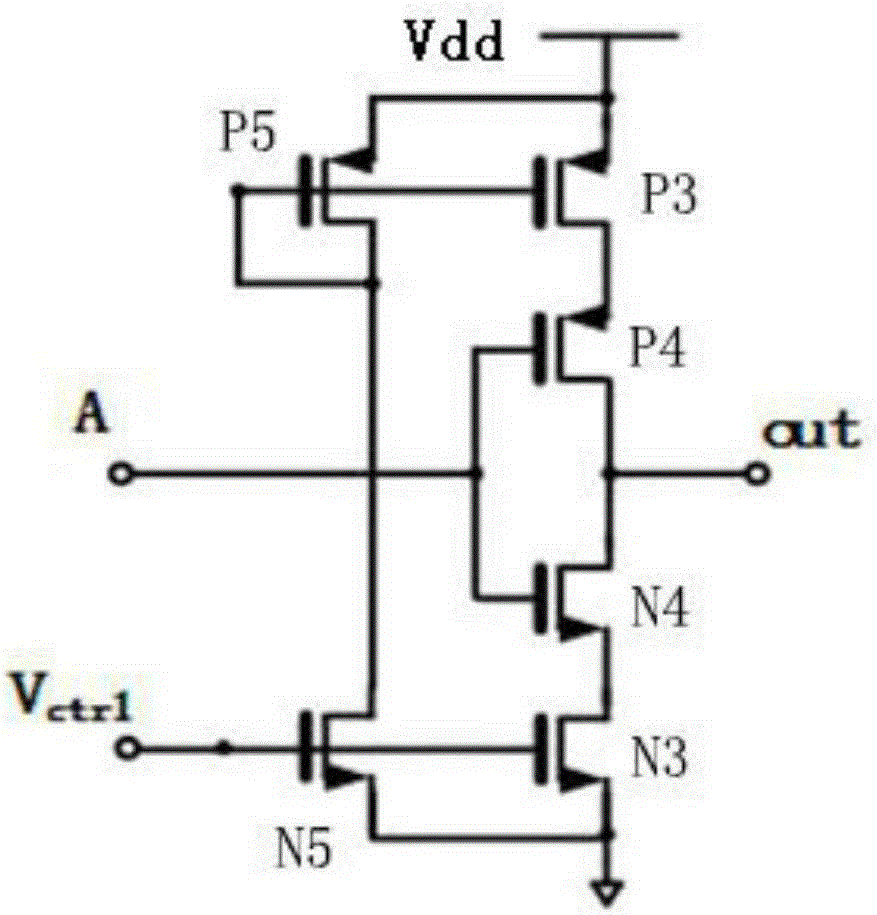

[0024] The structure and principle of the physically unclonable chip circuit in the embodiment of the present invention are as follows: Figure 1 to Figure 3 shown.

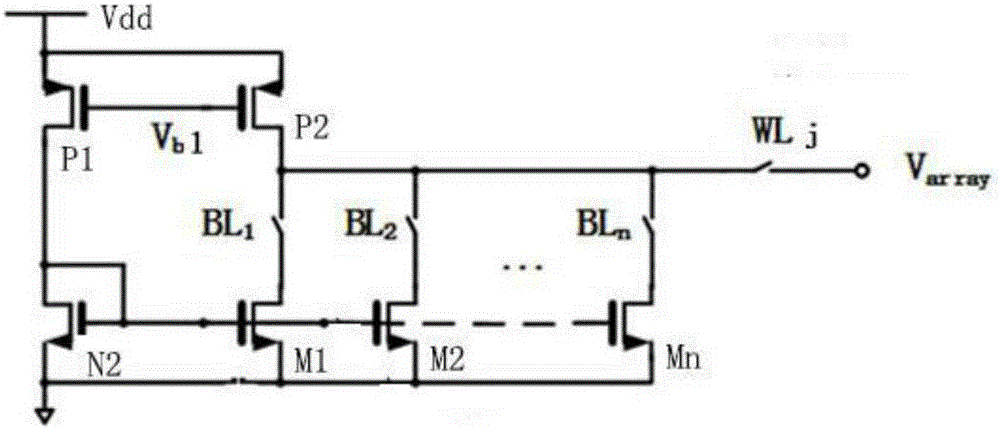

[0025] The physical non-clonable chip circuit and architecture of the embodiment of the present invention are as follows: figure 1 As shown, the physical non-clonable chip circuit consists of M rows and N columns of MOSFET arrays operating in the sub-threshold region and an automatic zero-calibration comparator. The array is composed of M×N minimum size NMOS with PMOS as the load.

[0026] The input signal of the physically unclonable chip circuit will select a row address port WL after being decoded by the decoder. j and a column address port BL i . by selected BL i and selected WL j One of the corresponding NMOSs can be turned on, and this NMOS will form a unipolar CMOS amplifier with the load PMOS in the row. The MOSFET array is connected from V array The terminals output voltages with different voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com