Chip automatic test method used for multi-temperature test

An automatic test, multi-temperature technology, applied in the direction of electronic circuit testing, etc., can solve the problems of inability to realize multi-temperature automatic control, a large number of temperature adjustment data collation, etc., to achieve the effect of automatic chip testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

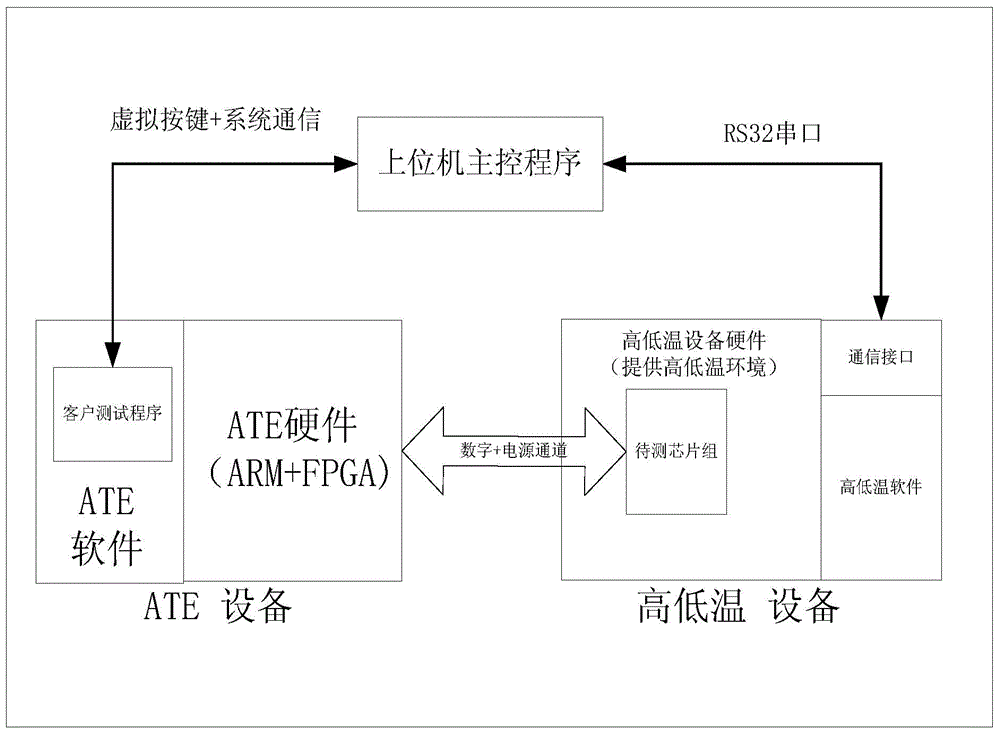

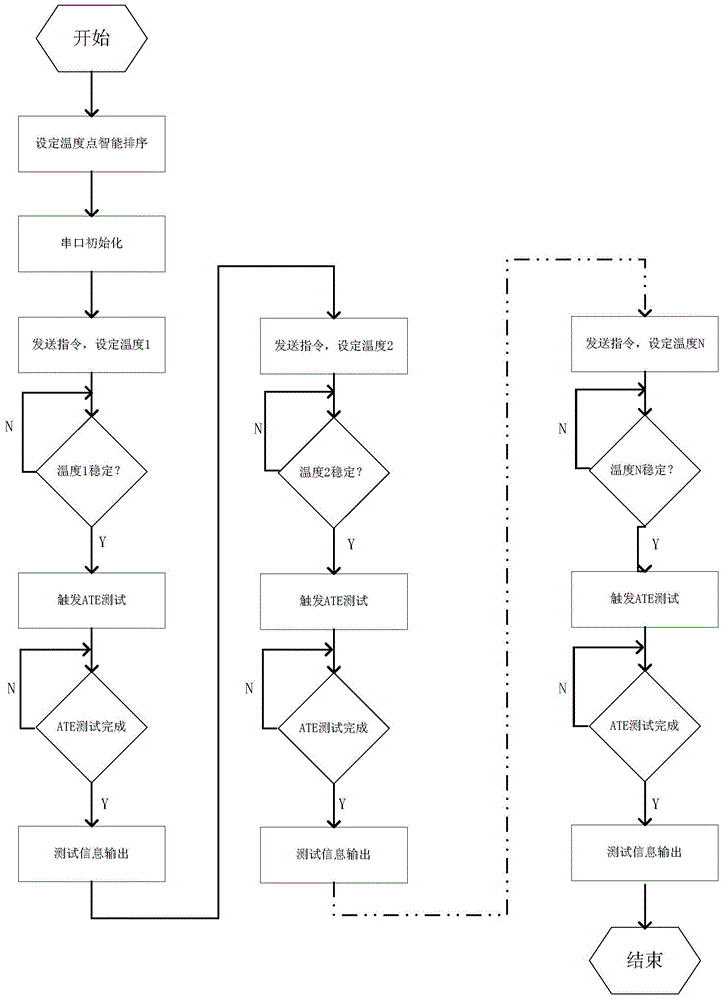

[0043] Please refer to figure 1 Shown is a block diagram of the hardware structure adopted for realizing the present invention. As shown in the figure, general-purpose ATE equipment is used for test stimulus provision and result measurement, because ATE secondary development is more convenient, and most IC design companies have ready-made ATE equipment. Choose a high and low temperature box as the ambient temperature supply device (must have a communication interface such as serial port or GPIB). The host computer software is used to control the ATE equipment and high and low temperature boxes. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com