Frequency domain implementation method of high-speed high-order FIR filter used for FPGA

An implementation method and filter technology, applied in the direction of impedance network, digital technology network, electrical components, etc., can solve the problem of FPGA resource consumption and processing speed, and achieve the elimination of zero padding delay phenomenon, solve resource consumption, and improve processing speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

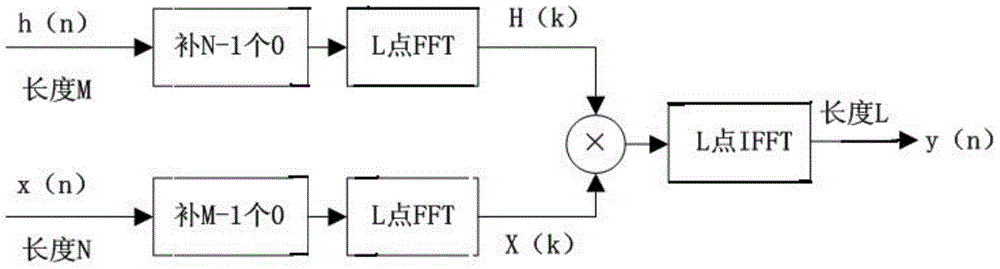

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the object, technical solution and advantages of the present invention clearer, the real-time solution of the present invention will be further described in detail below in conjunction with embodiments and drawings.

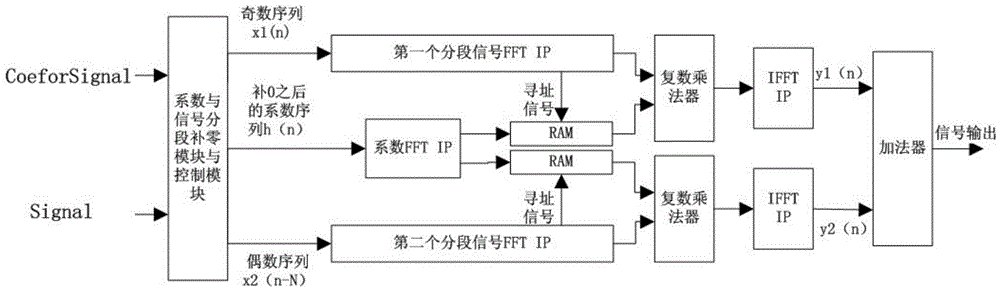

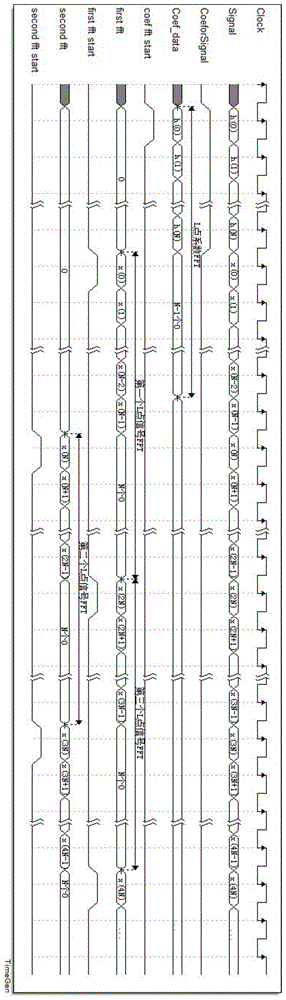

[0036] The invention provides a method for implementing a high-speed high-order FIR filter in the FPGA in the frequency domain. The method improves the problem that the data cannot be processed in real time due to time-consuming zero padding when the convolution operation is processed in the frequency domain. , changing the conventional scheme of using one FFTIP to process the sequence to use two FFTIPs to operate on the input data, the sequence timing is as follows image 3 shown. This method is suitable for systems whose coefficients are real or complex integers, for very high-order systems, for pulse compression systems, and for systems with configurable coefficients.

[0037] The technical solution of the present invention will be des...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com