Embedded system on chip for accelerating Cholesky decomposition

A system-on-chip and embedded technology, applied in the direction of complex mathematical operations, etc., can solve problems such as long calculation time, achieve shortened operation time, and simple read and write control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

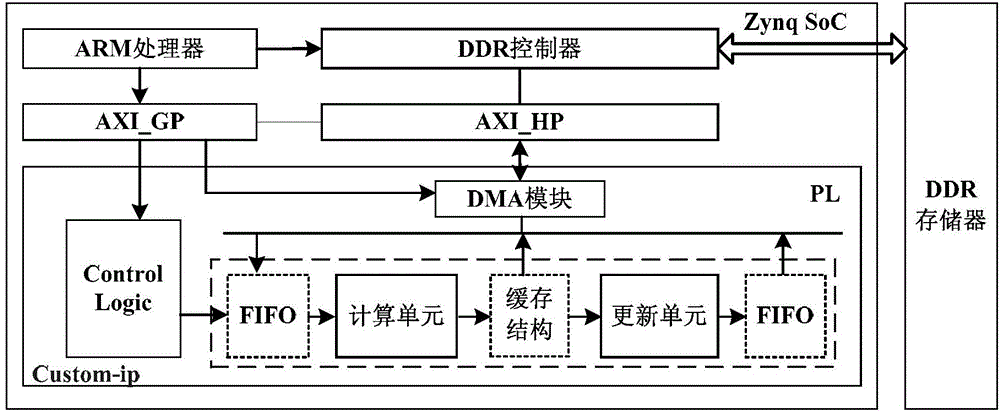

[0014] Specific implementation mode one: combine figure 1 , figure 2 Illustrate this embodiment mode, a kind of embedded system on chip that realizes Cholesky decomposition of acceleration, mainly comprises following module:

[0015] ARM processor module, used for task scheduling of the entire computing process;

[0016] DDR control module, used to control data reading and writing of external DDR memory;

[0017] The Programmable Logic module, referred to as the PL module, is used to read the value of the positive definite symmetric matrix from the external storage, perform Cholesky decomposition, obtain the lower triangular matrix and store it in the external storage;

[0018] The AXI bus module is used for information transmission between the PL module and the ARM processor module.

specific Embodiment approach 2

[0019] Specific implementation mode two: the PL module described in this implementation mode includes:

[0020] The Control Logic sub-module is used to receive the control information of the ARM processor module, coordinate the calculation work of the calculation unit and the update unit, and control the data reading and writing work of the internal RAM storage sub-module;

[0021] The DMA sub-module is used to control the data transmission between the PL module and the external memory;

[0022] The Cholesky decomposition sub-module is used for Submatrix-Cholesky decomposition of positive definite symmetric matrices and internal data caching.

[0023] The Submatrix-Cholesky decomposition sequence is shown in Table 1,

[0024] Table 1 Submatrix-Cholesky decomposition sequence table

[0025]

[0026]

[0027] Other steps are the same as in the first embodiment.

specific Embodiment approach 3

[0028] Specific implementation mode three: an embedded system-on-chip that accelerates the realization of Cholesky decomposition described in this implementation mode,

[0029] Described Cholesky decomposition submodule comprises:

[0030] The calculation unit is used for the calculation operation of the column when the positive definite symmetric matrix is decomposed by Submatrix-Cholesky;

[0031] The internal RAM cache unit is used to store the result data calculated by the calculation unit, which is convenient for the update unit to directly call from it;

[0032] The update unit is used to update the columns when the positive definite symmetric matrix is decomposed by Submatrix-Cholesky, and completes the update process of all columns after the calculation column;

[0033] The FIFO unit is used to cache the initial data of the Cholesky decomposition sub-module and the calculation result of the update unit, so as to facilitate the realization of the streaming mode of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com