A device-level automated test platform for sram type fpga and its test method

An automated testing and platform technology, applied in the direction of instruments, measuring electricity, measuring devices, etc., can solve the problems of inability to realize continuous download of multiple programs and automated testing, and achieve the effect of high scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

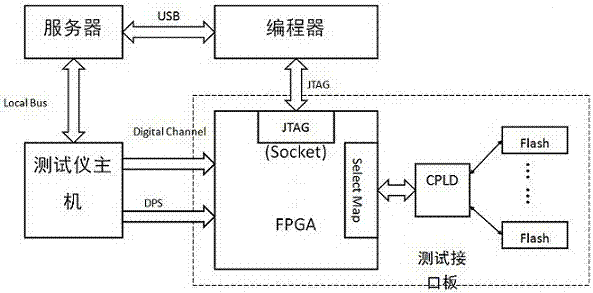

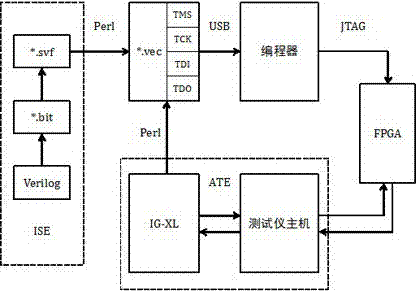

[0029] A device-level automated test platform applied to FPGA for aerospace models, characterized in that it includes: a server (Server), a programmer (Programmer), a tester host (Tester) and a test interface board (DIB); the test interface board Including the tested FPGA and auxiliary hardware configuration circuit;

[0030] The server and the programmer exchange data through a USB connection, the server connects to the tester host through a local bus (LocalBus) for data exchange, and the programmer configures the program of the FPGA under test through the JTAG interface of the FPGA under test , the host of the tester provides power to the FPGA under test through a DPS power supply module (Device Power Supply).

[0031] Power supply and measure its operating current, apply a test stimulus signal to the FPGA under test through a digital channel (Digita...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com