3D Integrated Circuit and Methods of Forming Same

A technology of integrated circuits and dielectrics, applied in the field of 3D integrated circuits and their formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The making and using of various embodiments of the present disclosure are discussed in detail below. It should be appreciated, however, that the embodiments provide many applicable concepts that can be implemented in a wide variety of specific contexts. The specific embodiments discussed are illustrative, and do not limit the scope of the disclosure.

[0030] Packages including hybrid bonding and methods of forming such packages are provided according to various exemplary embodiments. Intermediate stages in forming such a package are shown. Variations of the embodiments are discussed. Like reference numerals are used to refer to like elements throughout the various drawings and throughout the illustrative embodiments.

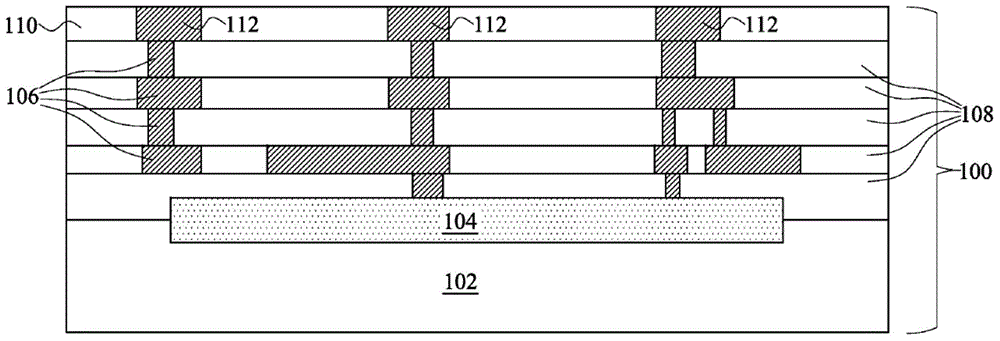

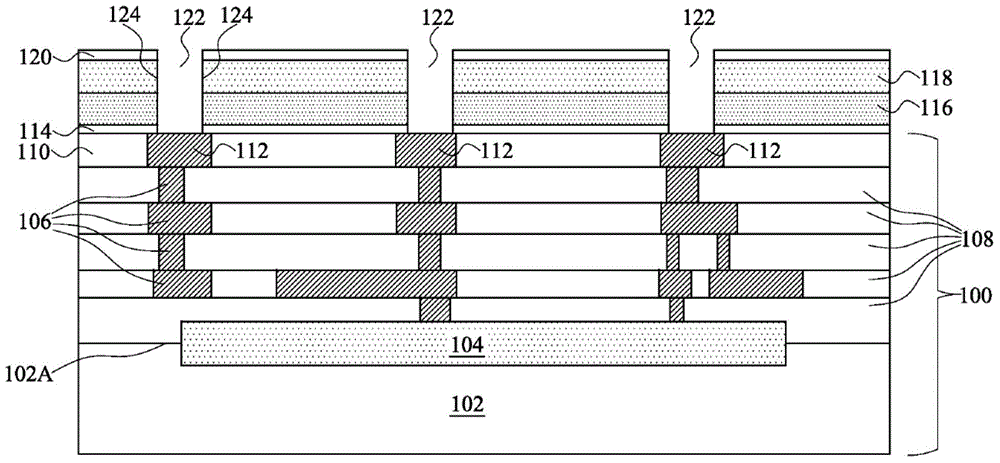

[0031] Figure 1 to Figure 5 Shown is a cross-sectional view of an intermediate stage in forming a packaged assembly according to some embodiments. refer to figure 1 , shows package assembly 100 . The package assembly 100 may include a device wafe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com