System and method for integrating extended double-precision 80-bit floating-point processing unit in processor

A technology of processing unit and integration method, applied in the direction of machine execution device, etc., can solve the problem of not giving FPU and processor whole point unit IU, cooperative work, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The present invention is described in further detail below in conjunction with accompanying drawing:

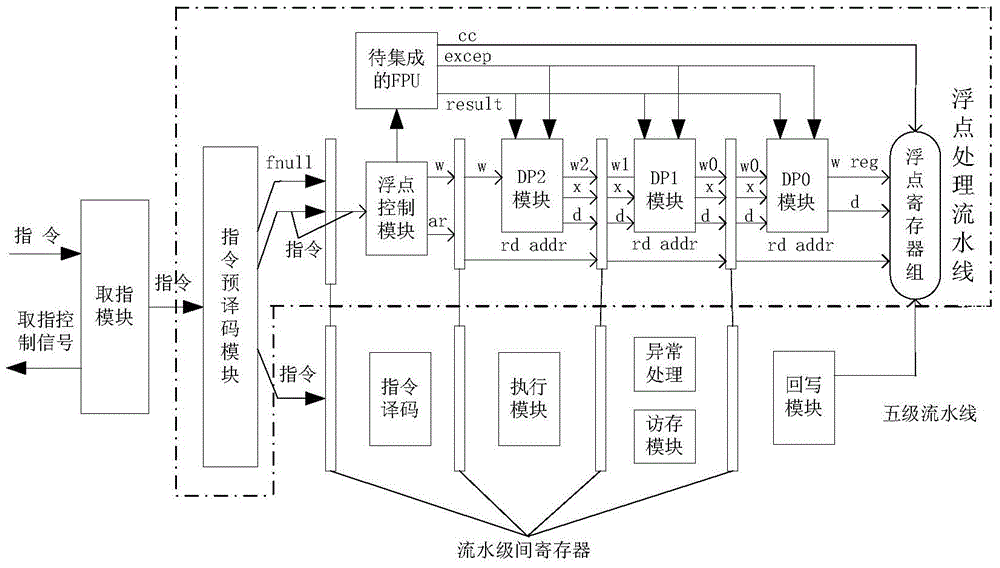

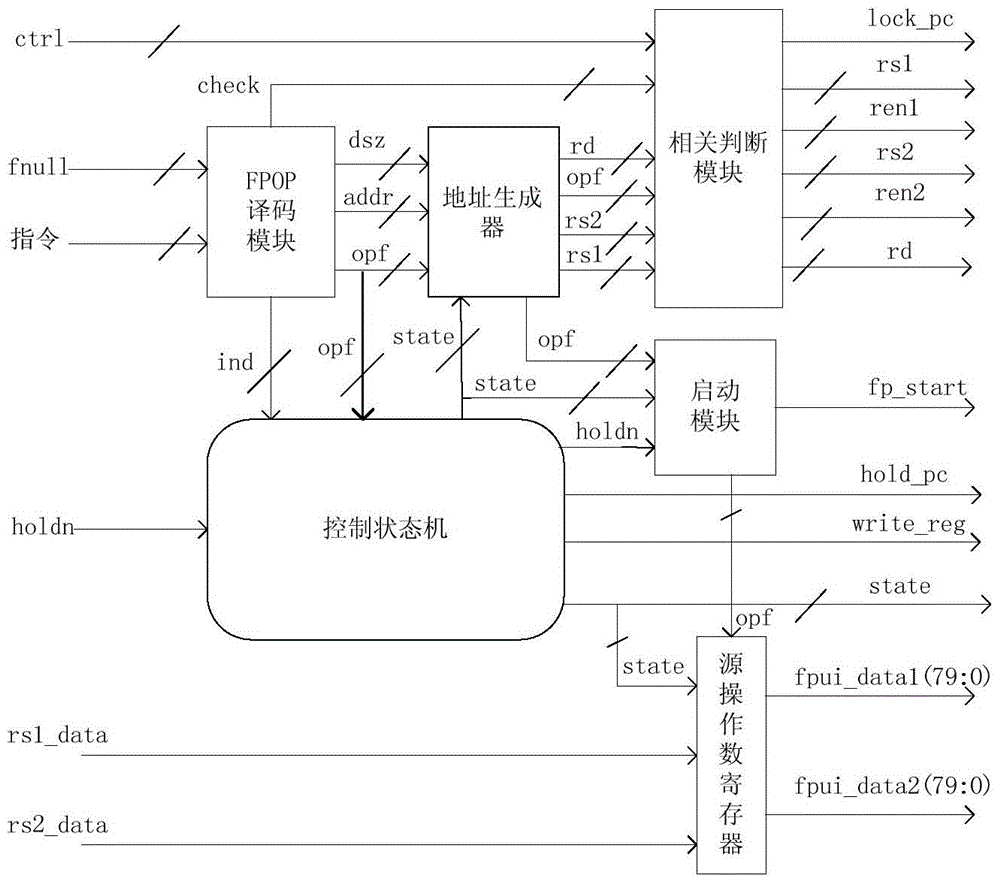

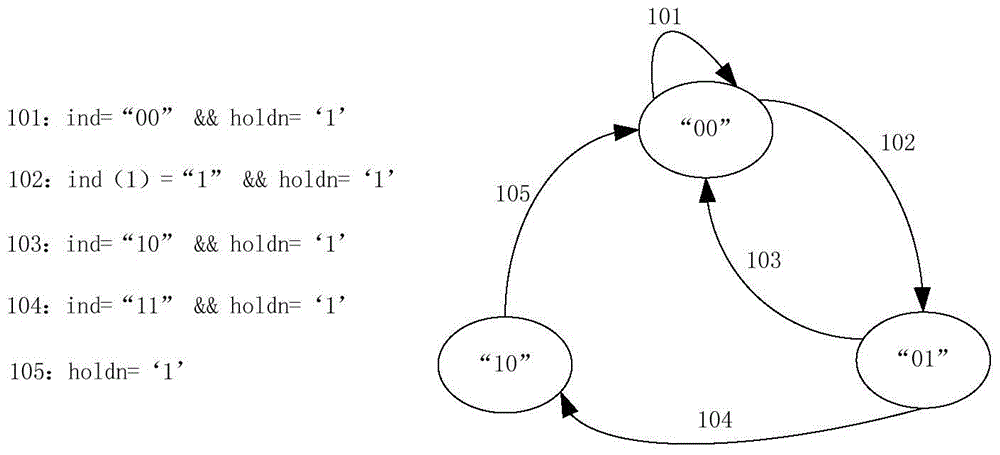

[0058] refer to figure 1 and figure 2 , the integrated system of the 80-bit floating-point processing unit of extended double precision described in the present invention comprises PC, five-stage pipeline, four-stage floating-point processing pipeline and instruction pre-decoding module, and four-stage floating-point processing pipeline comprises Floating-point control module, DP2 module, DP1 module, DP0 module, FPU to be integrated and floating-point register group, the output terminal of PC is connected to the input terminal of the instruction fetch module, and the output terminal of the instruction fetch module is connected to the instruction pre-decoding module The input terminal of the instruction pre-decoding module is connected with the input terminal of the five-stage pipeline and the input terminal of the floating-point control module respectively, and the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com