Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems such as the decline in the yield of multi-layer stacked chips and the increase in the number of semiconductor chips used

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

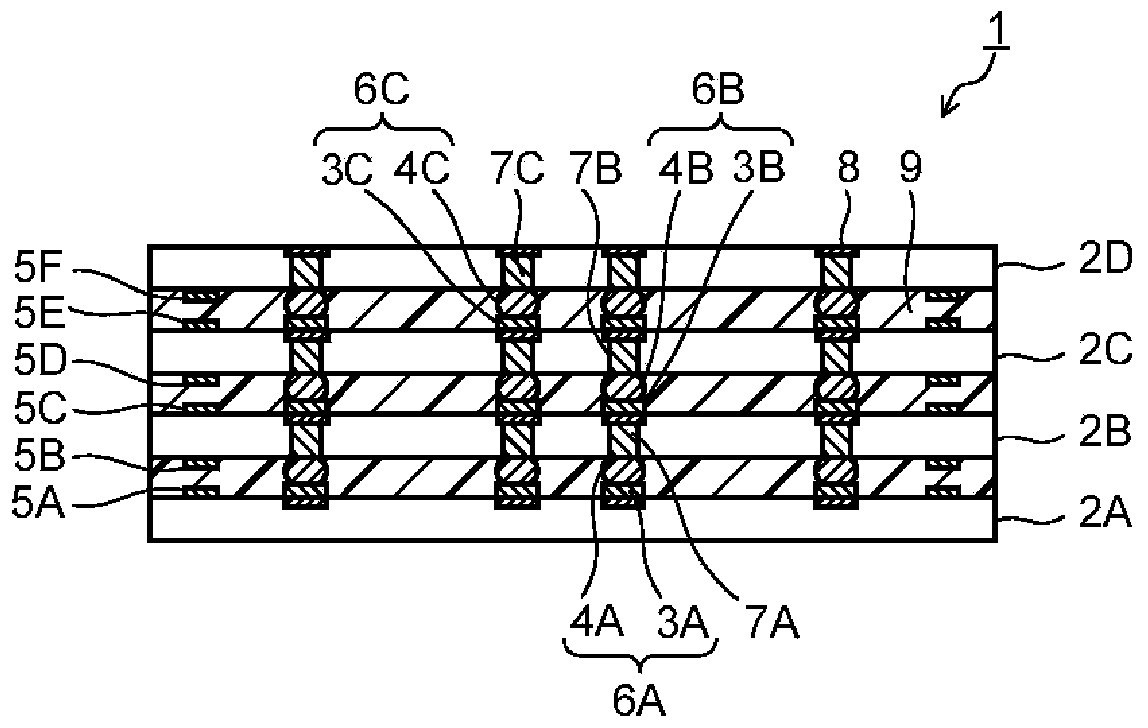

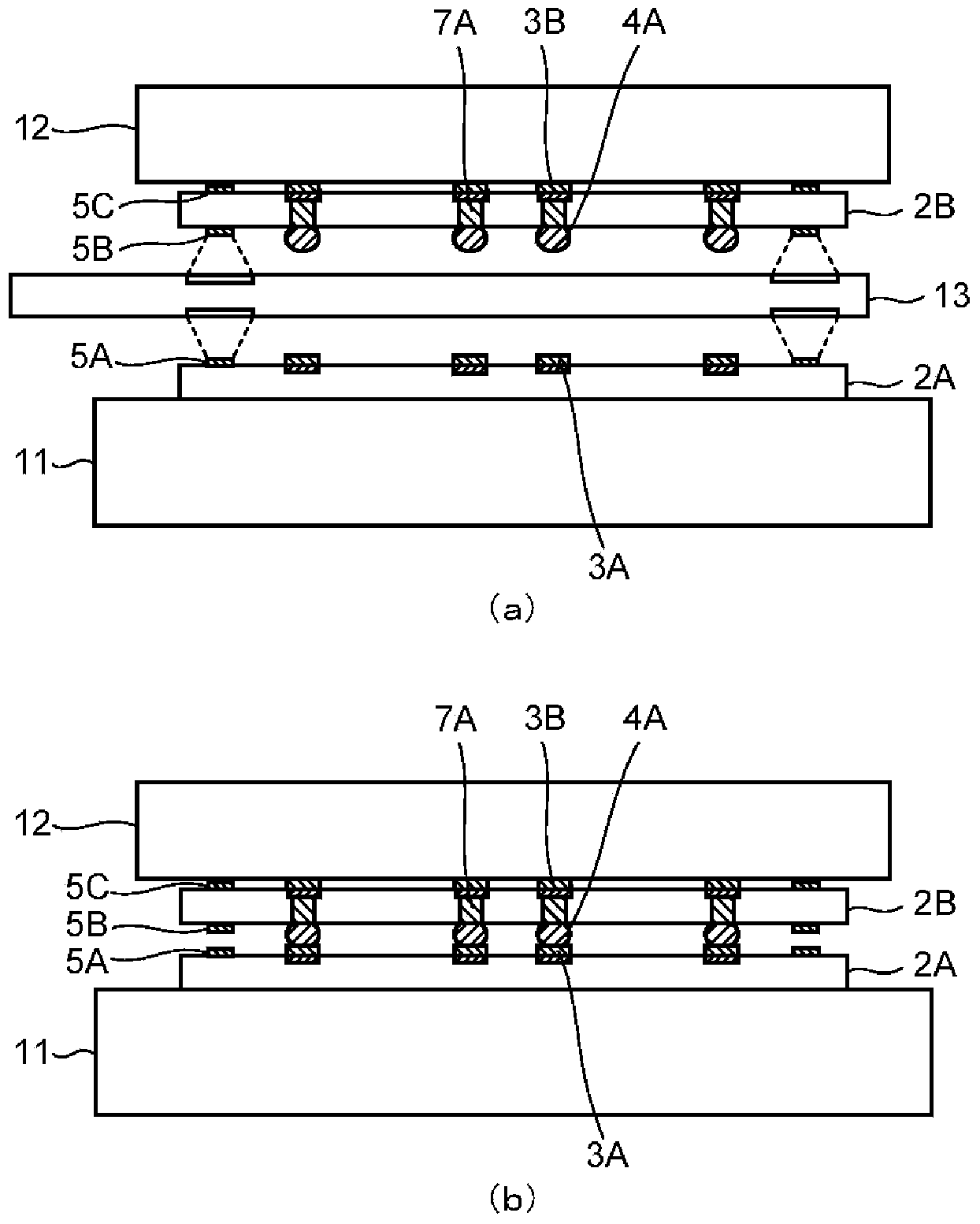

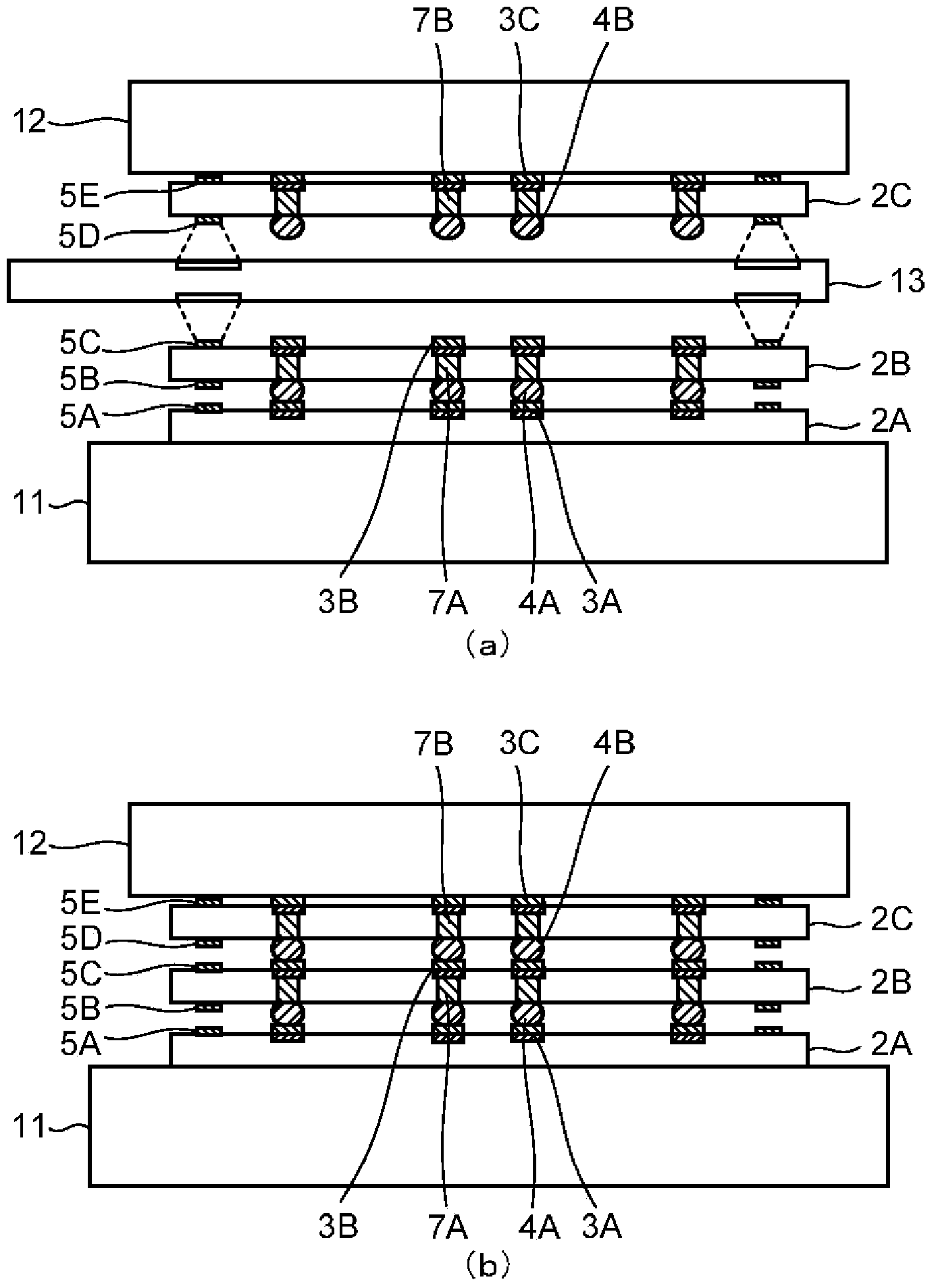

[0014] Next, a method of manufacturing a semiconductor device according to the embodiment will be described with reference to the drawings. First, refer to figure 1 A semiconductor device manufactured using the manufacturing method of the embodiment will be described. figure 1 The illustrated semiconductor device 1 includes a first semiconductor chip 2A, a second semiconductor chip 2B, a third semiconductor chip 2C, and a fourth semiconductor chip 2D. The second to fourth semiconductor chips 2B to 2D are sequentially stacked on the first semiconductor chip 2A. Here, although the semiconductor device 1 in which four semiconductor chips 2 are stacked is illustrated, the number of stacked semiconductor chips 2 is not limited thereto. The number of semiconductor chips 2 constituting the semiconductor device 1 (the number of stacks) may be three or more, and may be three or five or more.

[0015] On the upper surface (first surface) of the first semiconductor chip 2A, first bump...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com