Verilog coding method achieving ATE test waveform by adoption of FPGA

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In an application, it is necessary to apply any excitation vector signal waveform to any integrated circuit chip in an environment far away from the ATE to make it enter the corresponding circuit action state. Due to the movable limitation of ATE, we need to use FPGA instead of ATE to complete the above excitation vector waveform to achieve the application purpose.

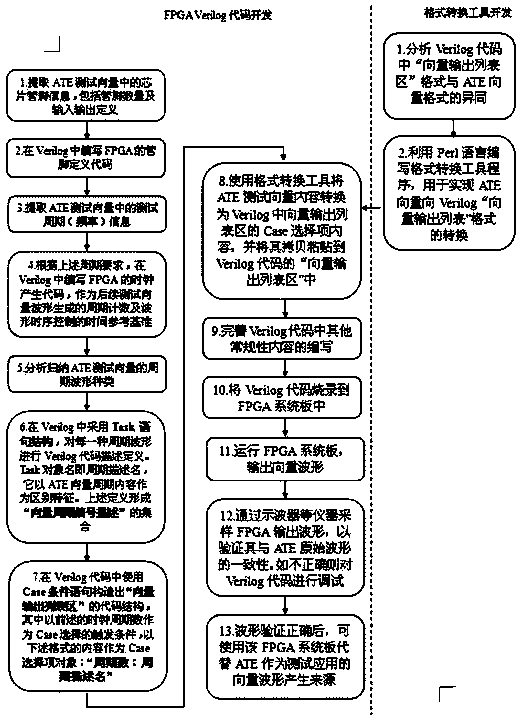

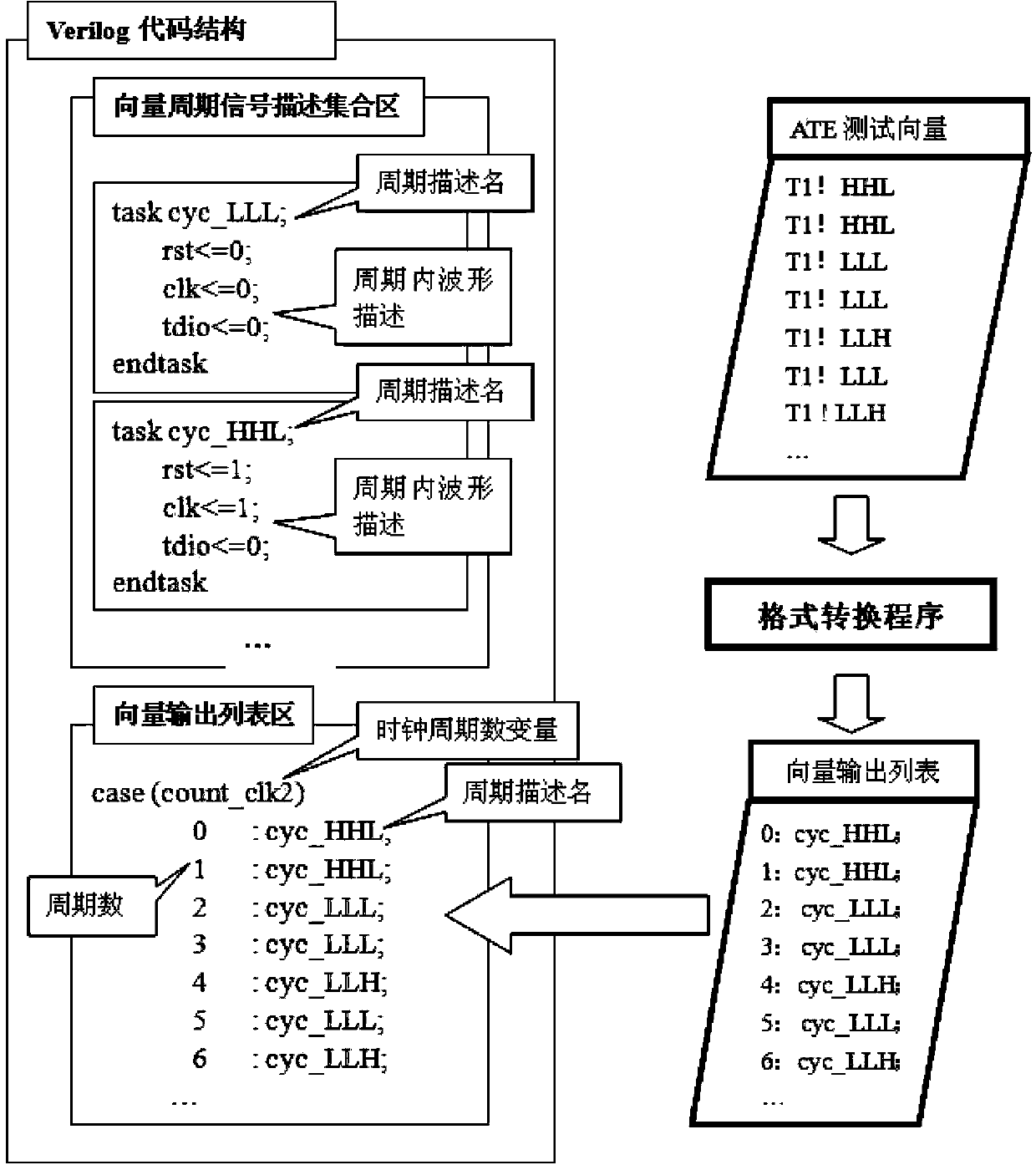

[0017] The method described in this invention was utilized in the development of FPGA vector generation in this application. figure 2 The application example is disclosed. In this application example, first analyze the ATE test vector to be applied, extract the required number of signal pins in the vector, and then define and describe the signal pins in the Verilog code. Then, the test cycle information used in the ATE vector is further extracted. According to the cycle information, a reference clock is designed in the Verilog code, which is used as the time reference for the cycle count and waveform timi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com