Self-inspection method and device of inter integrated circuit host and host

A technology of internal integrated circuits and hosts, applied in the field of communication, can solve problems that cannot be performed in real time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

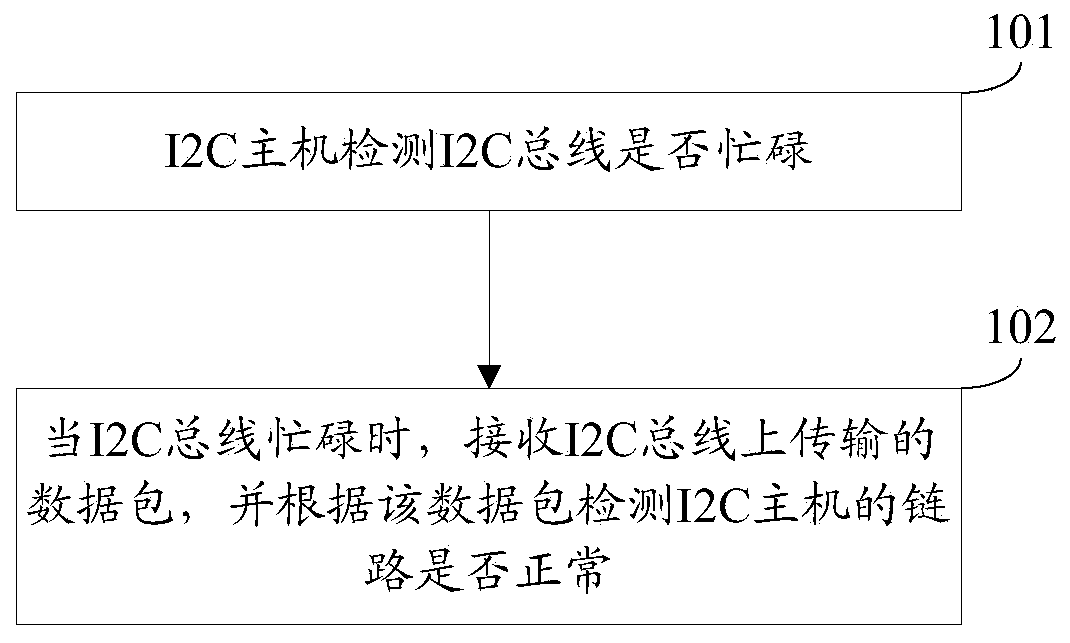

[0084] The embodiment of the present invention provides a self-test method of an I2C master, which can be executed when a standby I2C master establishes a connection with the I2C bus, see figure 2 , the method includes:

[0085] Step 101: the I2C master detects whether the I2C bus is busy.

[0086] Step 102: When the I2C bus is busy, receive a data packet transmitted on the I2C bus, and check whether the link of the I2C host is normal according to the data packet.

[0087] In the embodiment of the present invention, when the I2C bus is busy, the data packet transmitted on the I2C bus is received, and the link of the I2C host is detected according to the data packet, so the self-test of the I2C host does not need to wait until the I2C bus is idle. The embodiment of the present invention can be carried out in real time, avoiding the failure of the I2C master currently controlling the I2C bus existing in the prior art during the process of the I2C master waiting for self-inspec...

Embodiment 2

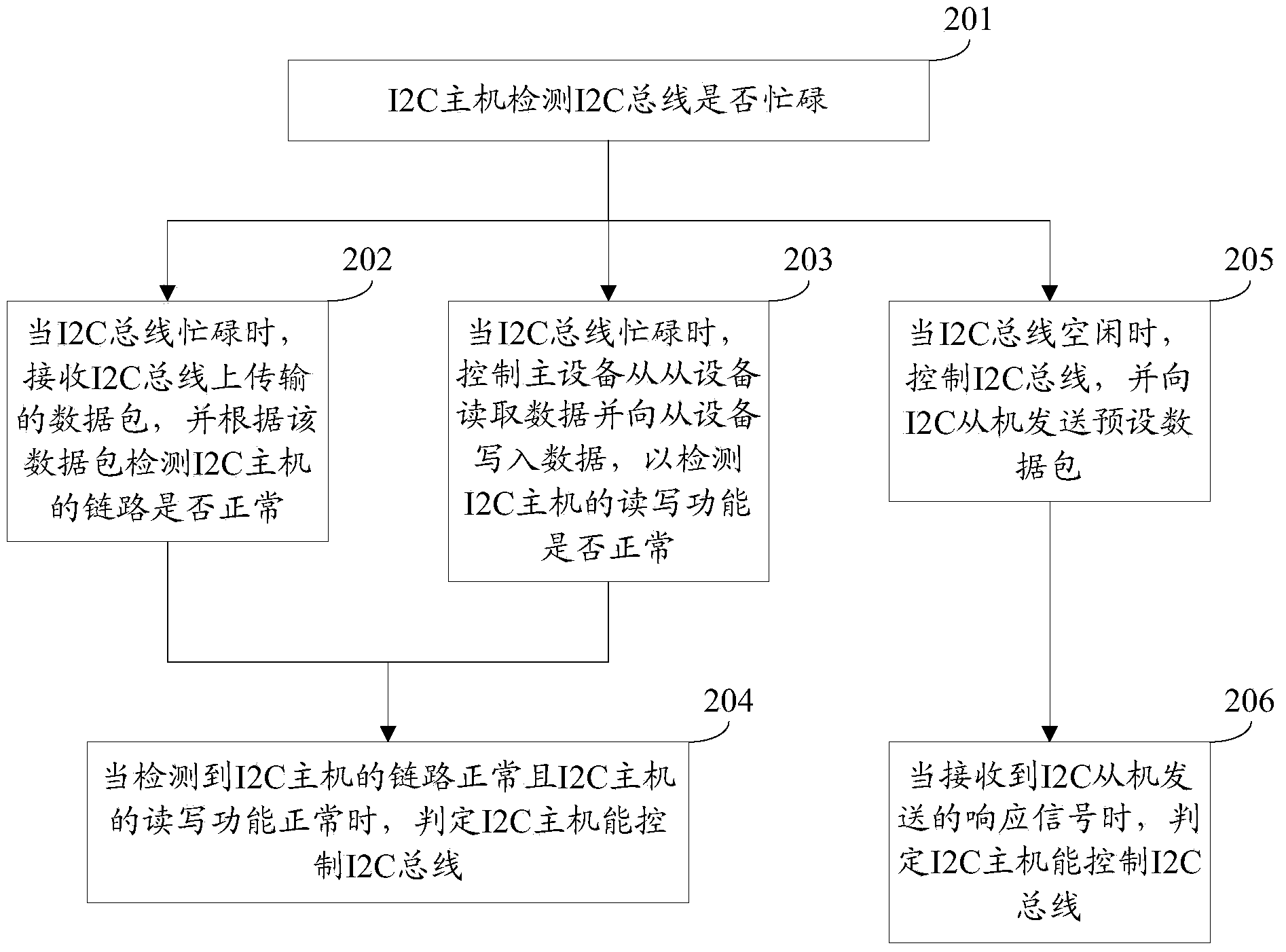

[0089] The embodiment of the present invention provides a self-test method of an I2C master, which can be executed when a standby I2C master establishes a connection with the I2C bus, see image 3 , the method includes:

[0090] Step 201: The I2C master detects whether the I2C bus is busy.

[0091] Specifically, this step 201 may include: detecting whether there is a level change on the SCL line within a period of a preset standard clock signal; if there is a level change on the SCL line within a period of a preset standard clock signal, Then the I2C bus is busy; if there is no level change on the SCL line within a period of a preset standard clock signal, the I2C bus is idle.

[0092] It should be noted that, according to the I2C protocol, when data transmission is performed on the I2C bus, that is, when the I2C bus is busy, there will be high and low levels on the SCL line, and the period of the level change is the period of the preset standard clock signal (The time interva...

Embodiment 3

[0124] The embodiment of the present invention provides a self-checking method of the I2C host, which is an improvement on the second embodiment. This method can be executed when the standby I2C host establishes a connection with the I2C bus. See Figure 5 , the method includes:

[0125] Step 301: The I2C master detects whether the I2C bus is busy. When the I2C bus is idle, execute step 302; when the I2C bus is busy, execute step 303.

[0126] Optionally, this step 301 may be the same as step 201 in Embodiment 2, which will not be described in detail here.

[0127] Step 302: Control the I2C bus, send a preset data packet to the I2C slave, and judge whether the I2C master can control the I2C bus according to whether a response signal sent by the I2C slave is received.

[0128] Optionally, this step 302 may include: when receiving the response signal sent by the I2C slave, determine that the I2C master can control the I2C bus; when not receiving the response signal sent by the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com