Array substrate, preparing method of array substrate and display device of array substrate

An array substrate and substrate technology, applied in the field of array substrates and their preparation methods, and display devices, can solve problems such as light leakage, poor orientation of liquid crystal molecules, and easy light leakage of data lines, etc., so as to improve light transmittance, increase contrast, and ensure quality Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

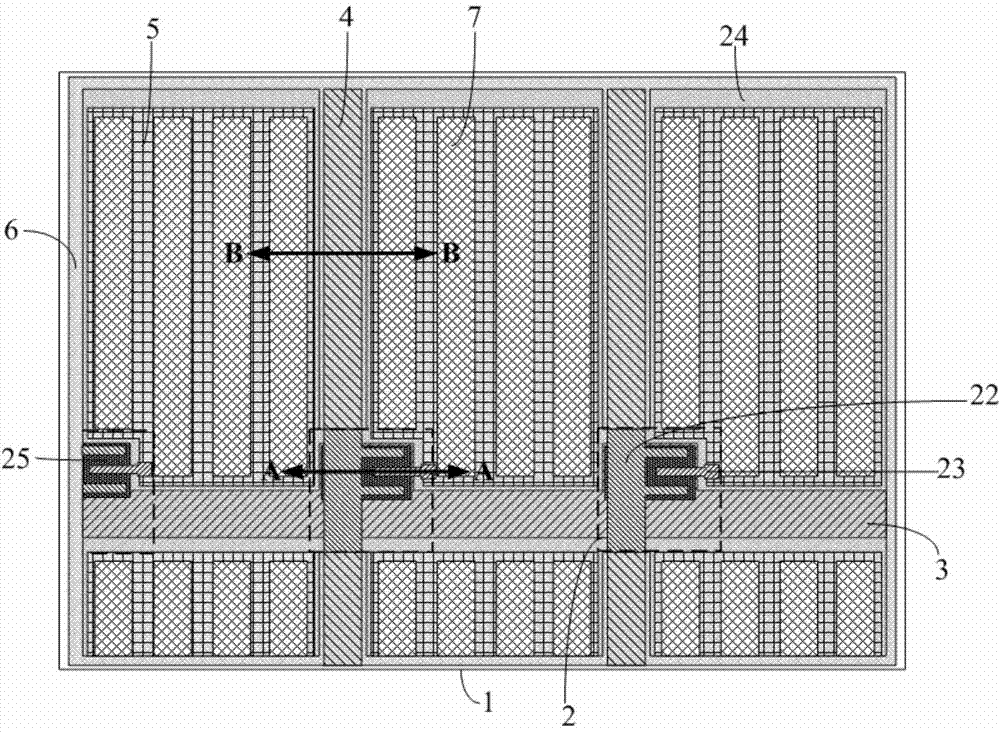

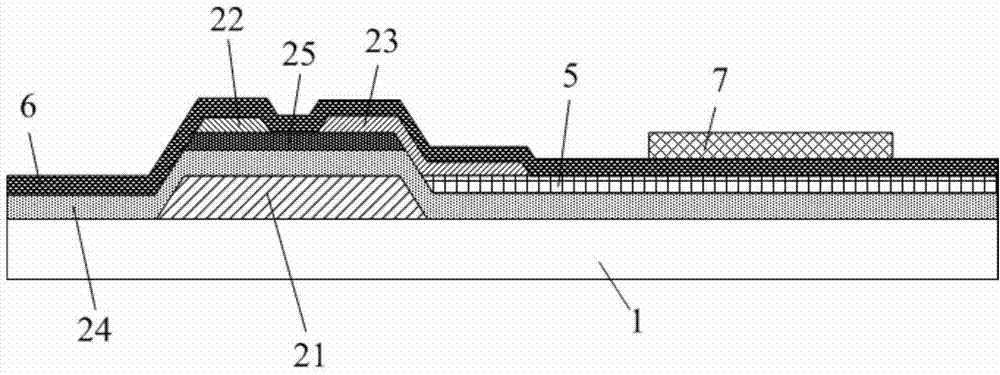

[0036] This embodiment provides an array substrate, such as figure 1 and figure 2 As shown, it includes: a substrate 1 and a thin film transistor 2 arranged on the substrate 1, a gate line 3 and a data line 4. The thin film transistor 2 includes a gate 21, a source 22 and a drain 23 arranged on the same layer, and a gate line 2 arranged on the gate. The gate insulating layer 24 between the electrode 21 and the source electrode 22 and the drain electrode 23, the gate electrode 21 is electrically connected to the gate line 3, the data line embedded area is arranged in the gate insulating layer 24, and the data line 4 is arranged in the data line embedded area , the data line 4 is electrically connected to the source 22 .

[0037] In addition, in this embodiment, the thin film transistor further includes an active layer 25 disposed between the source 22 and the drain 23 and the gate insulating layer 24 and corresponding to the gate 21 .

[0038] Wherein, the gate line 3 and th...

Embodiment 2

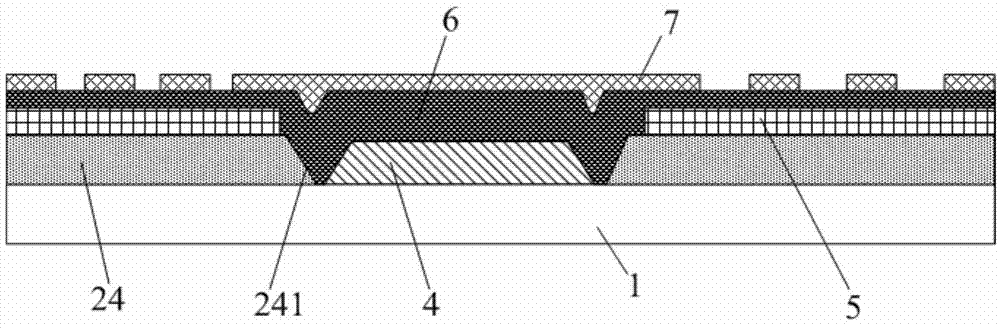

[0067] This embodiment provides an array substrate, and the difference from Embodiment 1 is that, as Figure 5 As shown, the strip-shaped groove 241 is opened on the surface layer of the gate insulating layer 24, and the depth of the strip-shaped groove 241 is smaller than the thickness of the gate insulating layer 24, the data line 4 is arranged at the bottom of the strip-shaped groove 241, and the height of the data line 4 is less than or equal to The depth of the strip groove 241. Such an arrangement also enables the data lines 4 to be completely embedded in the bar-shaped grooves 241 , so that the data lines 4 form only a small or no gap with respect to other regions in the pixel region.

[0068] Also, since the gridlines ( Figure 5 (not shown in ) is arranged under the gate insulating layer 24, so there is a thin layer of gate insulating layer 24 between the data line 4 and the gate 21 / gate line 3, and the thin layer of gate insulating layer 24 The thickness is the dif...

Embodiment 3

[0080] This embodiment provides an array substrate. The difference from Embodiment 1-2 is that the positions of the common electrode and the pixel electrode in the array substrate are interchanged, that is, the pixel electrode is arranged above the passivation layer, and the pixel electrode is a strip-shaped narrow a slit structure; and the common electrode is arranged between the gate insulating layer and the passivation layer, and the common electrode is plate-shaped.

[0081] Correspondingly, based on the preparation method of the array substrate in Embodiment 1, in the preparation method of the array substrate, the step of forming the pixel electrode (ie, step S4) and the step of forming the common electrode (ie, step S7) can be interchanged. .

[0082]Other structures, sizes, materials and manufacturing methods of the array substrate in this embodiment are the same as those in Embodiment 1 or 2, and will not be repeated here.

[0083] The array substrates in Examples 1-3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com