System and method for modeling printed circuit board level conducted electromagnetic interference

A technology of conducting electromagnetic interference and printed circuit boards, which is applied in the direction of program control devices, electrical digital data processing, software simulation/interpretation/simulation, etc. It can solve problems that affect the research and development cycle and cost, achieve optimal design, and improve system performance. , cost-saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] The present invention is a system for quantitative modeling and analysis of circuit board-level conduction electromagnetic interference. Interference performance is optimized.

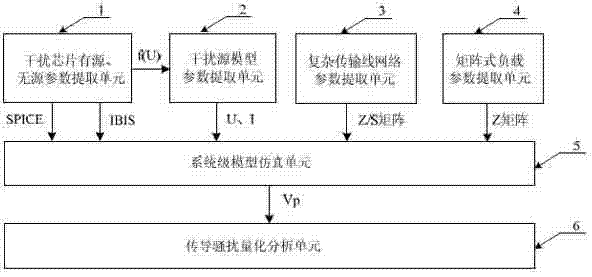

[0046] figure 1 It is a circuit board-level conducted electromagnetic interference modeling system of the present invention. The system includes an interference chip active and passive parameter extraction unit 1, a complex transmission line network parameter extraction unit 2, a matrix load parameter extraction unit 3, and an interference source model parameter extraction unit. Unit 4, system-level model simulation unit 5 and conduction disturbance quantitative analysis unit 6.

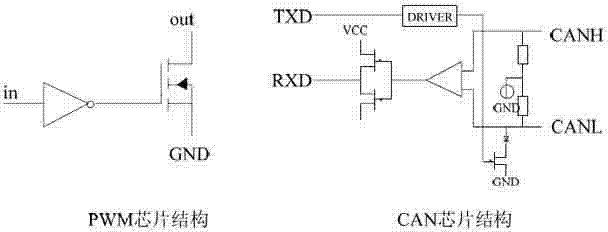

[0047] The power module on the circuit board is equivalent to a harmonic voltage source. The main harmonics of the power module are the switching frequency and its higher harmonics. The actual switching frequency of the power module is 300kHz, so it is equivalent to the harmonic source of 300kHz and 600kHz.

[0048...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com