Bus architecture for multiprocessor parallel communication

A multi-processor and communication bus technology, which is applied in the field of multi-processor parallel communication bus architecture, can solve communication problems and other problems, achieve the effect of maximizing investment benefits, improving communication efficiency, and saving R&D investment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0013] Serial bus: As the speed of the parallel bus increases, the problem of crosstalk between lines becomes more prominent. In recent years, with the development of high-speed serial communication technology, from the early RS485 up to 10M to the current LVDS close to 2G, the serial communication rate has been greatly improved, and the serial communication bus has also emerged.

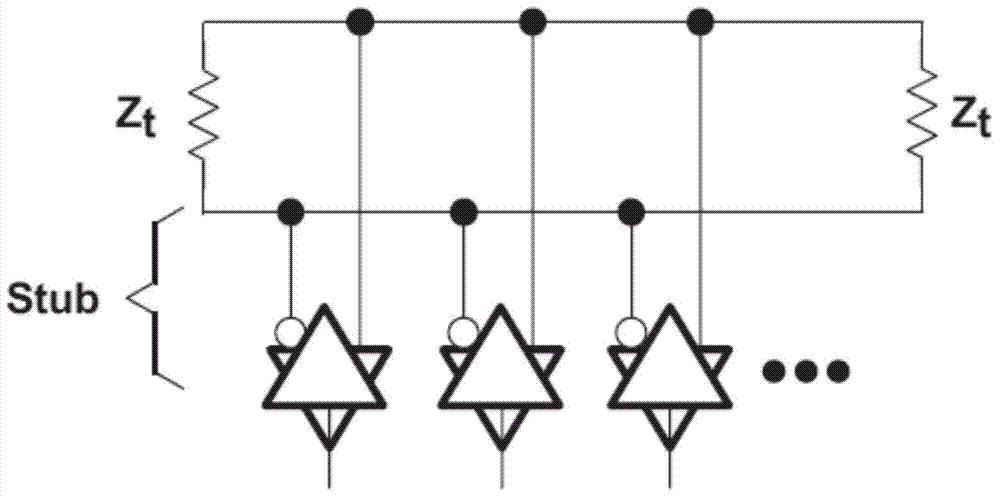

[0014] The serial bus of the bus architecture of the multiprocessor parallel communication adopts the serial bus technology of multi-transmitting nodes, which can realize one transmission and multiple receptions, and the maximum rate can reach 500Mbps. In this structure, multiple transceivers can be connected to the same bus, such as figure 1 As shown, the sending and receiving state can be controlled by controlling the sending and receiving direction, thus allowing two-way half-duplex communication.

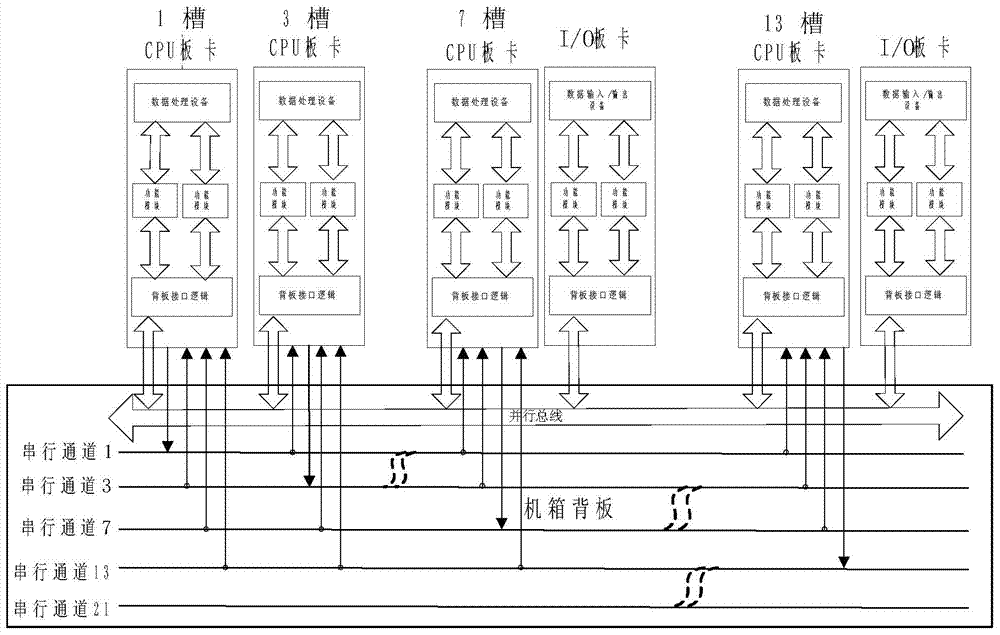

[0015] The bus architecture of multiprocessor parallel communication, the communication bus inclu...

Embodiment 2

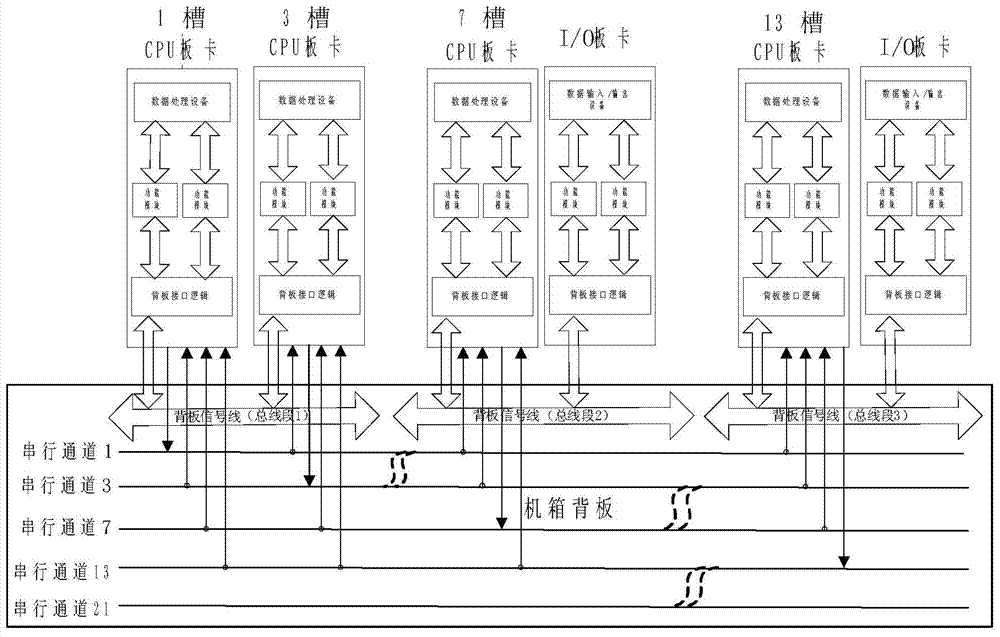

[0020] Such as image 3 As shown, in order to further mitigate bus contention, the figure 2 The shown multi-processor parallel communication bus architecture is based on a plurality of serial buses, and a parallel bus is also provided. The parallel bus is N sections of sub-buses arranged in parallel, and each section of sub-buses is connected to at least one CPU plug-in.

[0021] The traditional shared parallel bus is segmented (divided into 3 segments), and each segment is a fully functional parallel bus backplane structure, forming a segmented multi-bus architecture from the perspective of the overall chassis.

[0022] In the application of HVDC power transmission system, it is most common that there are less than or equal to 3 CPUs in one chassis. Then, if a high-speed parallel bus is divided into three parallel buses, most of the application needs will be met. Of course, a spare sub-bus can also be added for use when more processors are used. Physically speaking, if the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com