CDR-based clock synthesis

一种时钟、数据的技术,应用在时钟合成领域

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

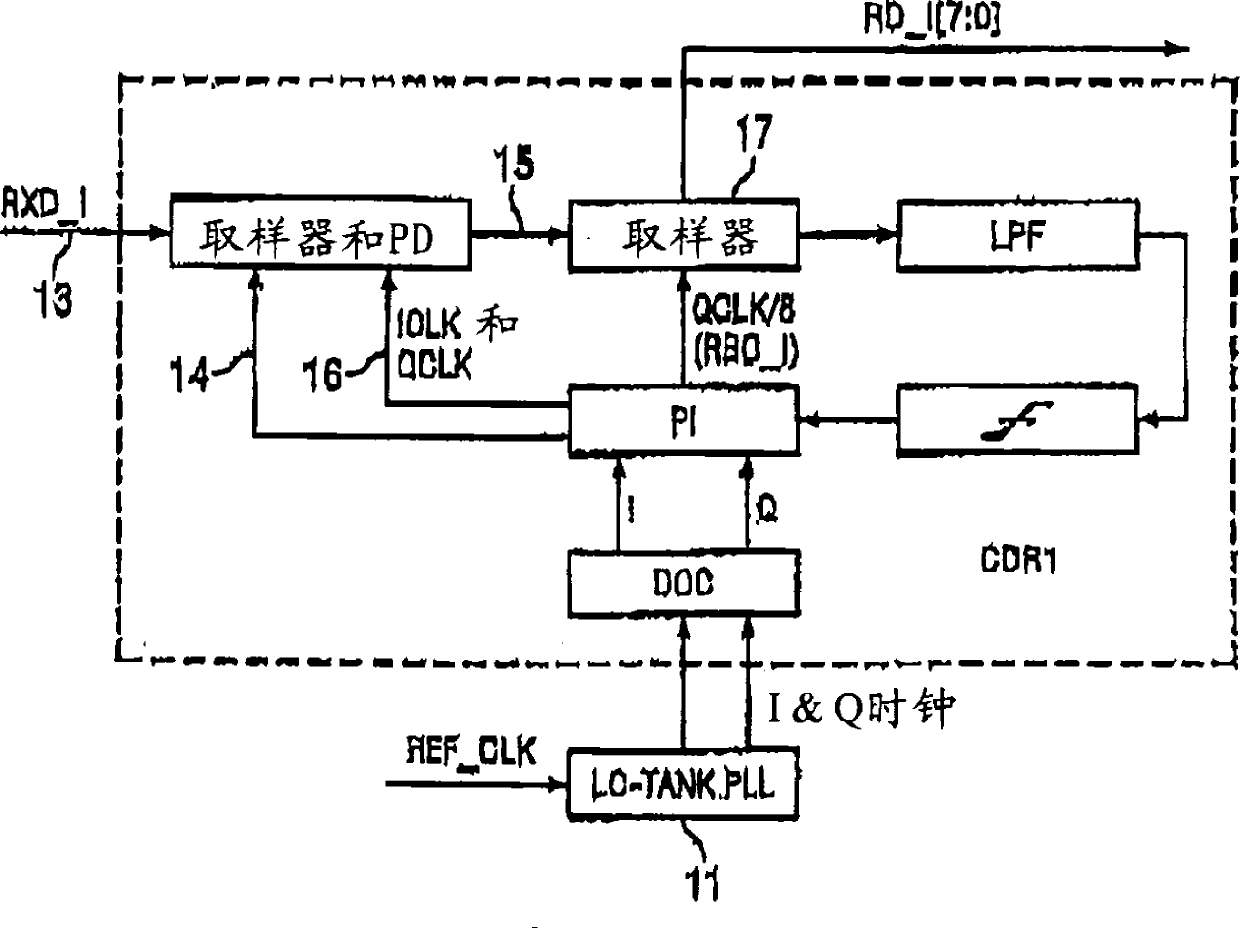

Image

Examples

Embodiment Construction

[0011] A clock source can be viewed as a periodic data stream; when given a data rate f D , with frequency f D A clock source of / (2n) can be viewed as a periodic data stream with a percentage transition density of (100 / n). For example, clocks with frequencies of 1.25 GHz (n=1), 625 MHz (n=2) and 417 MHz (n=3) can all be considered as 2.5 Gb / s periodic data streams with switching densities, respectively 100%, 50% and 33%.

[0012] Performing CDR on a clock input is equivalent to restoring its frequency while attenuating its noise content. Unlike random data, clocks have a fixed (i.e., generally do not change over time) transition density, so CDR circuits are able to use lower bandwidth than is required for random data, thereby performing phase noise removal at lower frequencies .

[0013] figure 2 The diagrams illustrate relevant parts of a serial data radio in accordance with a preferred embodiment of the present invention. A noisy external clock source (TXCKSRC) can b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com