Array substrate and manufacturing method thereof

A technology of an array substrate and a manufacturing method, which is applied in the display field, can solve the problems of widening the width of the wiring area, reducing the number of signal lines, and increasing the number of drivers, and achieves the effects of extending the length, reducing the manufacturing cost, and increasing the length and resistance of the signal lines Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

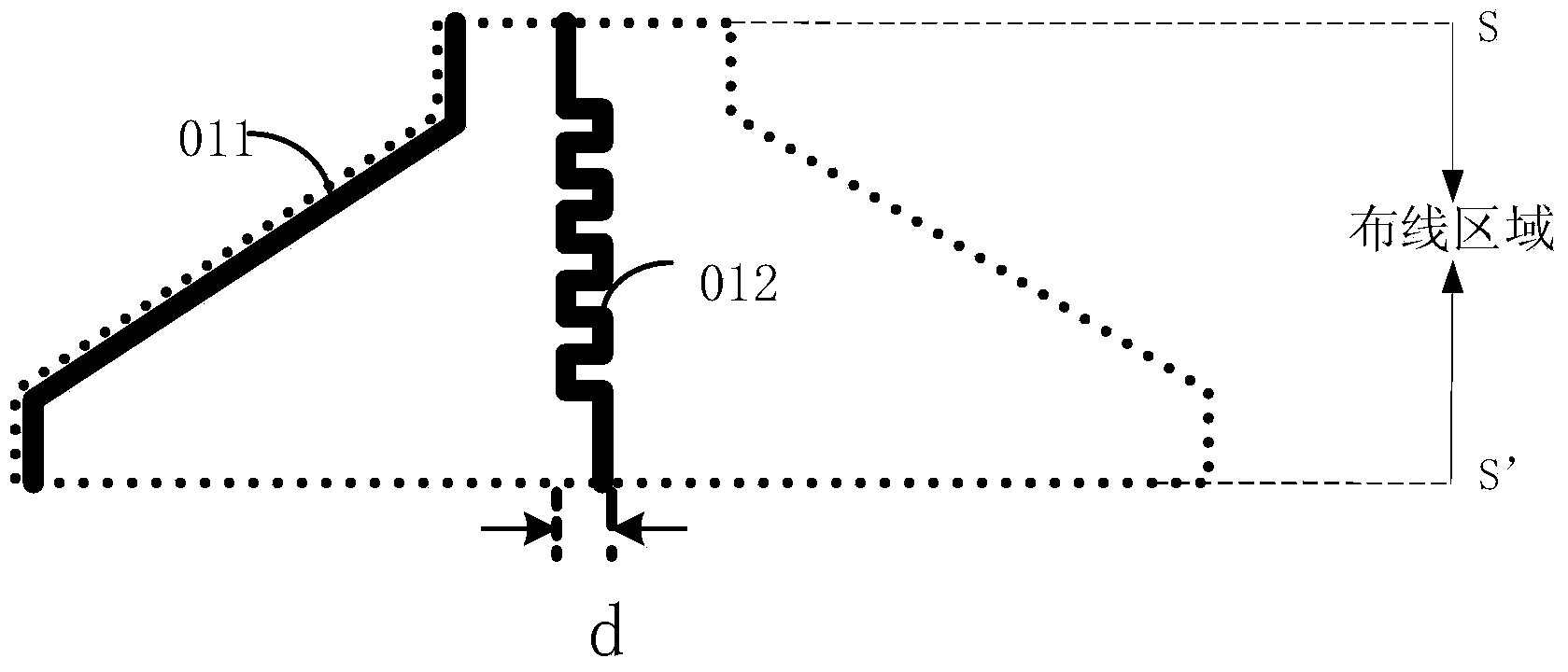

[0075] The array substrate of this embodiment includes a plurality of wiring areas arranged in the non-display area, and several signal lines are arranged in the wiring areas, and at least part of the signal lines in each wiring area are connected in series by wires located in different layers. formed; the resistance difference between any two signal lines in the same wiring area is within the threshold range.

[0076] The array substrate is divided into a display area located in the middle, which is usually also referred to as an AA area, and a non-display area located at the periphery of the display area. Usually, after the array substrate is assembled into a display device, the non-display area is covered by a frame of the display device. There are multiple wiring areas in the non-display area; several signal lines are arranged in each of the wiring areas; the signal lines can be gate lines or data lines; the signal lines are located in the part of the wiring area It is us...

Embodiment 2

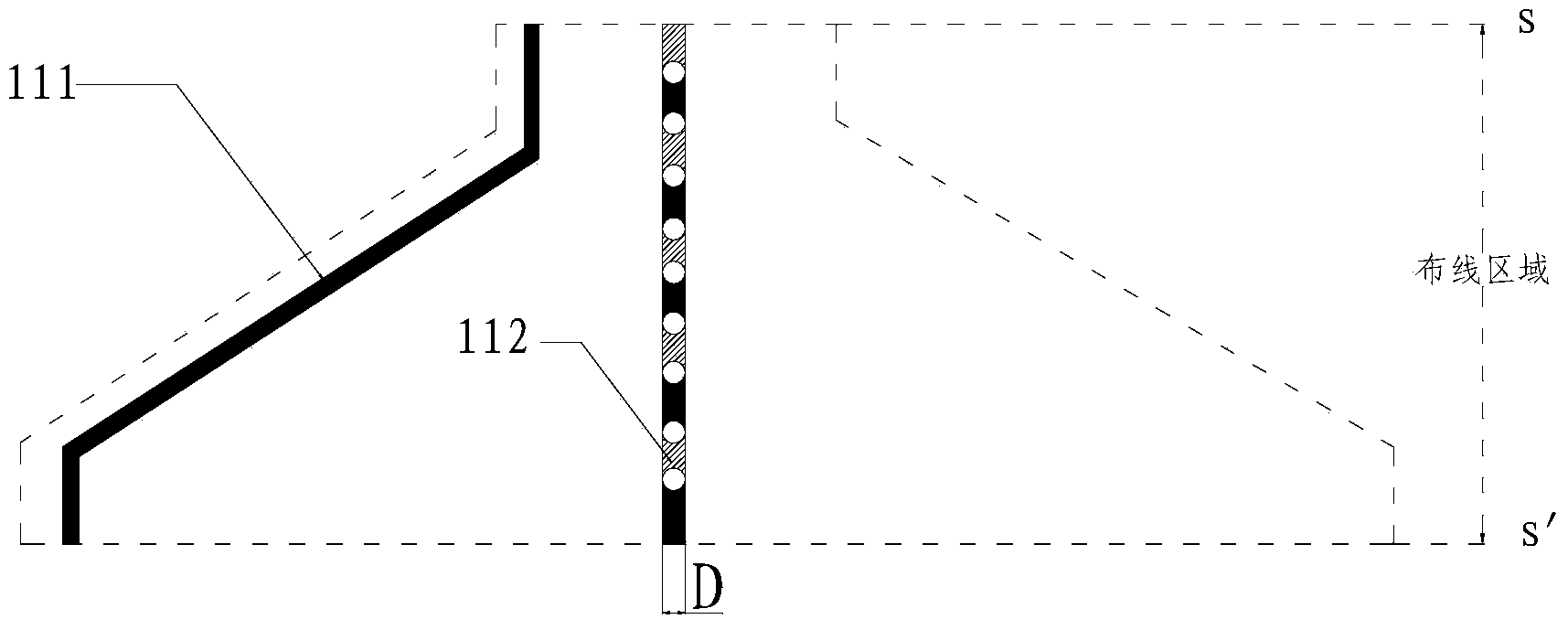

[0094] The array substrate of this embodiment includes a plurality of wiring areas arranged in the non-display area, and several signal lines are arranged in the wiring areas, and at least part of the signal lines in each wiring area are connected in series by wires located in different layers. formed; the resistance difference between any two signal lines in the same wiring area is within the threshold range. The wires of different layers are sequentially connected according to the extending direction of the signal wires.

[0095] specific as Figure 6 As shown, the array substrate includes a pixel electrode layer, a gate line metal layer, and a source-drain metal layer. specific as Figure 6 The middle signal line is located in the non-display area of the array substrate, including signal line 210, signal line 220, and signal line 230. If traditional single-layer wiring is used, since the signal line 210 is located at the outermost periphery of the connecting wiring area...

Embodiment 3

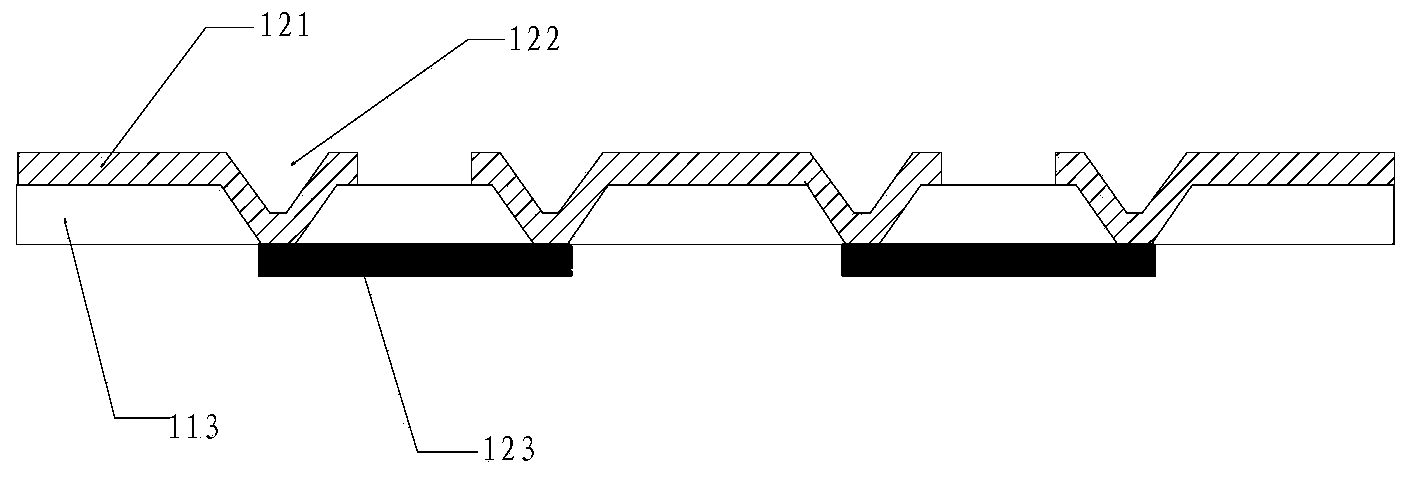

[0103] This embodiment provides a manufacturing method of an array substrate, the manufacturing method comprising: forming a signal line located in a non-display area and connected to a gate line or a data line, and the signal line is formed by connecting wires located in different layers in series; Wherein, the signal lines are located in the wiring area of the non-display area of the array substrate; and the resistance difference between any two signal lines in the same wiring area is within a threshold range.

[0104] Specifically, wires located in different layers to form signal wires include at least the following two structures:

[0105] In the first type, in at least one conductive layer used to form wires in the array substrate, several wires are formed, and the wires located in different layers are correspondingly connected in series.

[0106] The second type is to form a wire corresponding to a signal line in the conductive layer used to form wires on the array s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com