Simulation device of load data processor and implementation method thereof

A load data and simulation device technology, applied in the field of satellite testing, can solve problems such as the difficulty in fault location of satellite data transmission subsystems, and achieve the effects of improving test efficiency, reducing test costs, and improving safety and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

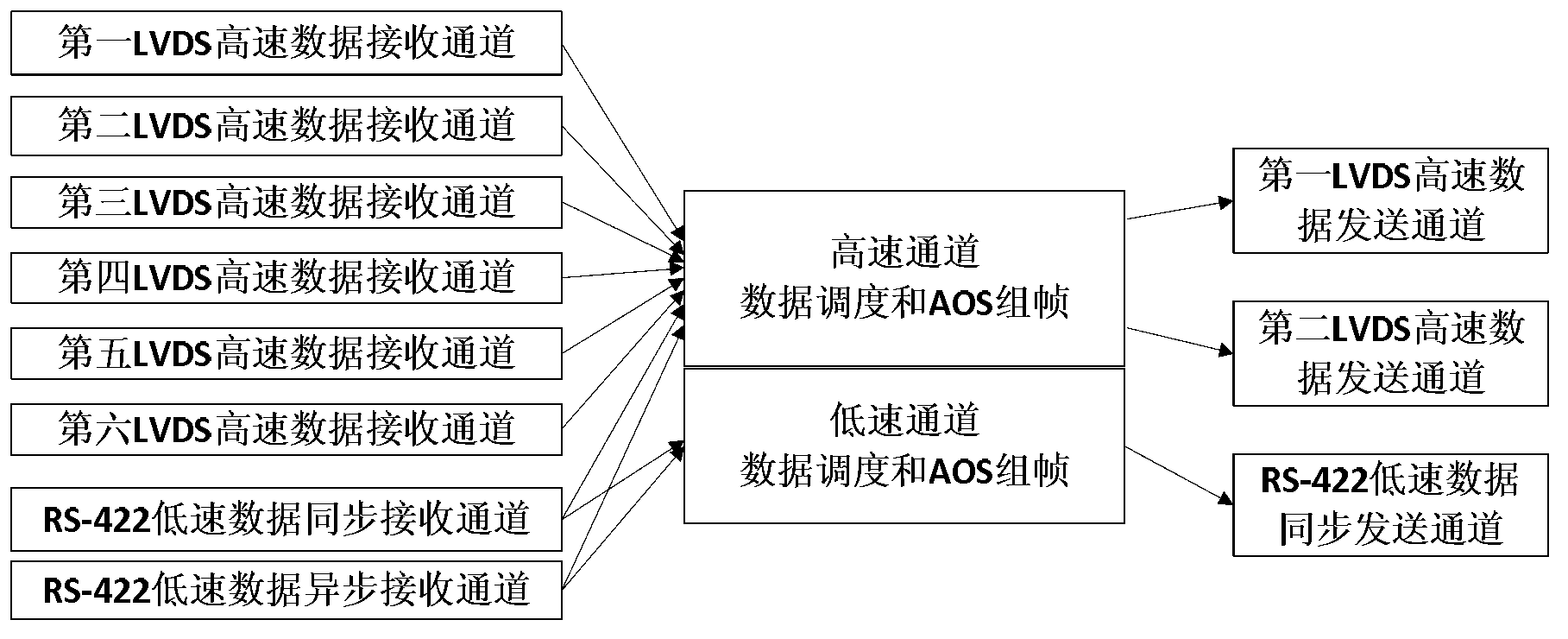

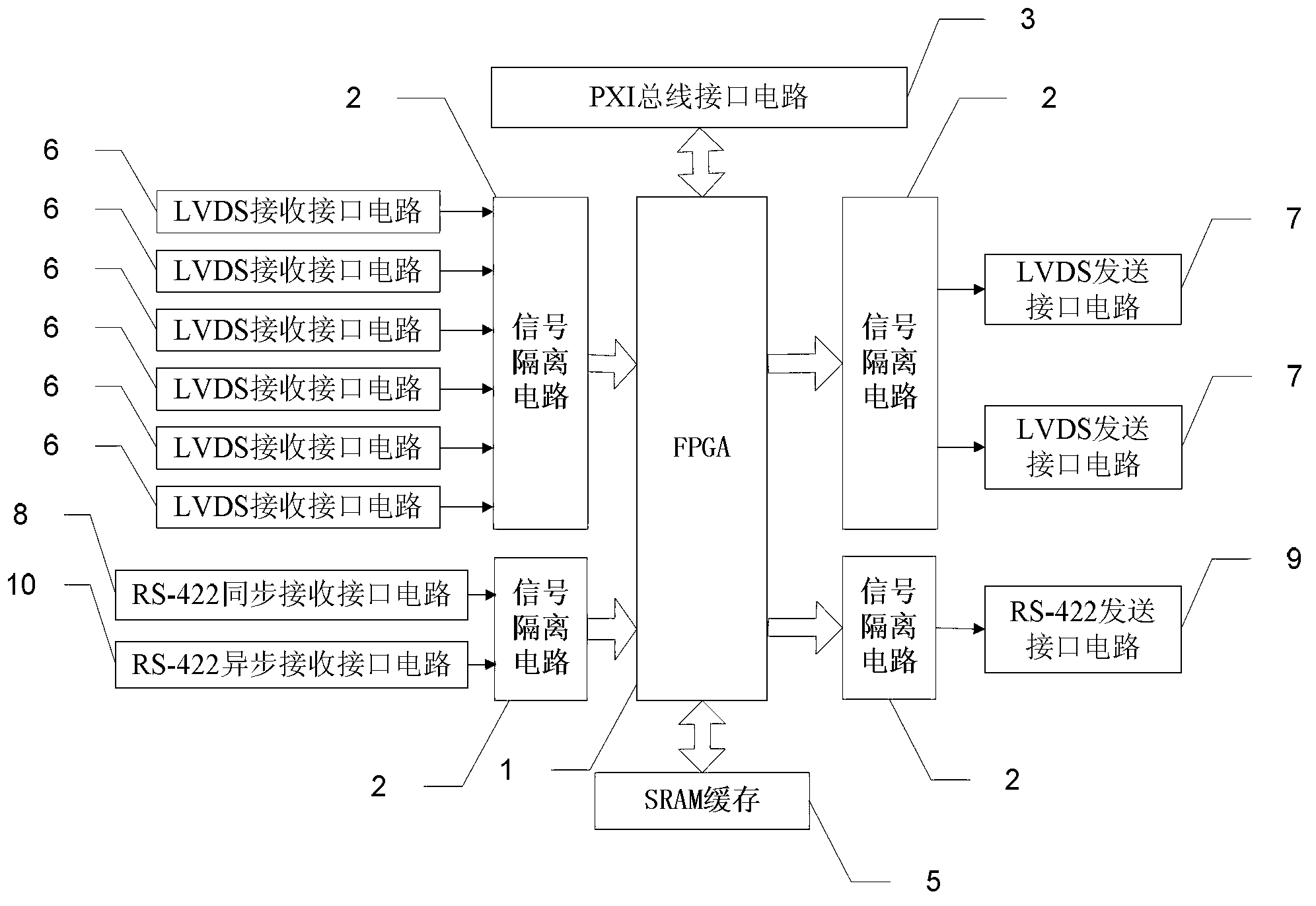

[0028] Specific implementation mode one: the following combination figure 2 Describe the present embodiment, the load data processor simulation device described in the present embodiment, it comprises FPGA1, signal isolation circuit 2, PXI bus interface circuit 3, LVDS receiving and sending interface circuit and RS-422 data receiving and sending circuit, described The LVDS receiving and sending interface circuit includes 6 LVDS receiving interface circuits 6 and 2 LVDS sending interface circuits 7, and the RS-422 data receiving and sending circuit includes 1 RS-422 synchronous receiving interface circuit 8, 1 RS-422 Asynchronous receiving interface circuit 10 and 1 RS-422 sending interface circuit 9,

[0029] The high-speed data signal output terminals of the 6 LVDS receiving interface circuits 6 are respectively connected to the high-speed data signal input terminals of the first signal isolation circuit 2, and the high-speed data signal output terminals of the first signal ...

specific Embodiment approach 2

[0033] Specific implementation mode two: the following combination figure 2 Describe this embodiment mode, this embodiment mode will further explain Embodiment 1, and it also includes SRAM cache 5, and the buffer data input and output end of FPGA1 is connected to the buffer data input and output end of SRAM cache 5.

[0034] In this embodiment, the load data of most channels can be cached by the FPGA internal FIFO, and the load data of individual large-capacity and high-speed channels need to pass through the SRAM cache 5 to avoid frame loss. After the cached data is scheduled and framed by AOS, the The LVDS receiving and sending interface circuit and the RS-422 synchronous data receiving circuit send out.

specific Embodiment approach 3

[0035] Embodiment 3: This embodiment further describes Embodiment 1. The transmission rate of the LVDS receiving and sending interface circuit is greater than or equal to 96 Mbps.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com