Thin film transistor, array substrate, manufacturing method and display device

A technology of thin-film transistors and array substrates, applied in the display field, can solve problems such as poor pixel bright spots, incomplete etching, and lower product quality levels, so as to reduce defective pixels, avoid bridging, and improve product yield.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0054] A preparation method of a thin film transistor, comprising the step of forming the source layer and the drain layer on different layers and forming the gate layer and the drain layer on the same layer.

[0055] A method for preparing an array substrate, including the above-mentioned method for preparing a thin film transistor.

Embodiment 1

[0057] A thin film transistor, comprising a substrate and a gate layer, a source layer, and a drain layer arranged on the substrate, the source layer and the drain layer are arranged on different layers, and the drain layer is provided in the same layer as the gate layer.

[0058] An array substrate, including the above-mentioned thin film transistor.

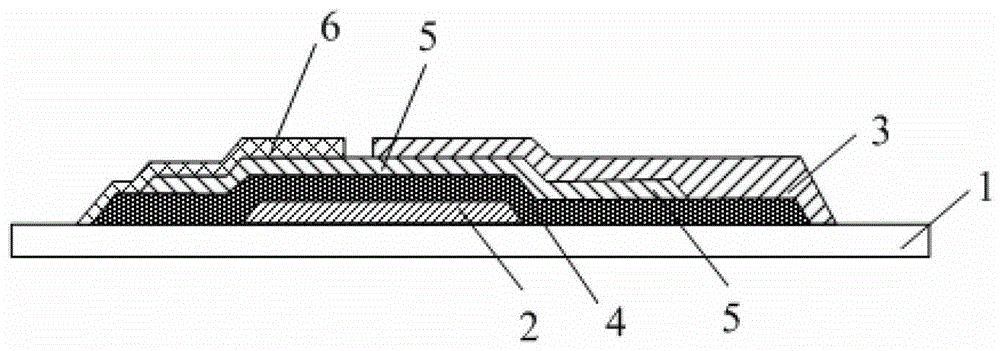

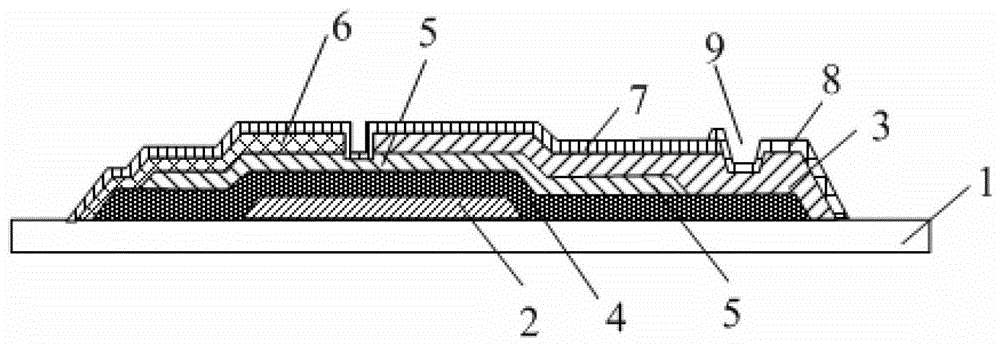

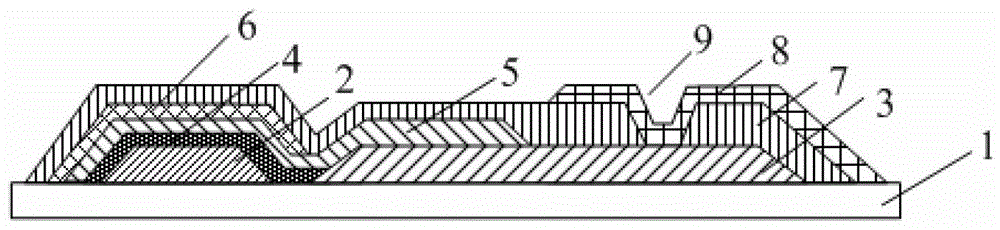

[0059] like figure 2 As shown, in the thin film transistor, the drain layer 3 and the gate layer 2 are arranged on the substrate 1 in the same layer, and there is a gap or gap between the drain layer 3 and the gate layer 2 trench; the source layer 6 is disposed above the gate layer 2, and a gate insulating layer 4 and a composite layer 5 are disposed between the source layer 6 and the gate layer 2, and the gate The electrode insulating layer 4 is disposed above the gate layer 2 and below the composite layer 5, and the composite layer 5 covers the gap or trench from the gate insulating layer 4 and partially extends to the dra...

Embodiment 2

[0087] The difference between this embodiment and Embodiment 1 lies in that the thin film transistor of this embodiment and the active layer in the corresponding array substrate are formed of amorphous silicon material.

[0088] In this embodiment, the composite layer includes an active layer and an ohmic contact layer disposed above the active layer, the active layer is formed of amorphous silicon material, and the thickness range of the active layer is The ohmic contact layer is formed of amorphous silicon material doped with phosphorus, and the thickness range of the ohmic contact layer is

[0089] For the preparation method of the thin film transistor array substrate in this embodiment, reference may be made to Embodiment 1 for details. The difference is that the step S3) is specifically: forming a pattern including a composite layer on the substrate after step S2), and the composite layer includes an active layer and an ohmic contact layer disposed above the active l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com