Single-deck capacitance electrode layout structure

A layout structure and capacitive technology, applied in the field of single-layer capacitive electrode layout structure, can solve problems such as poor line drawing effect, large power noise interference, unstable multi-finger touch detection, etc., and achieve signal strength Strong, improved signal resolution, improved scanning speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

[0011] see figure 1 and figure 2 , the embodiment of the present invention includes:

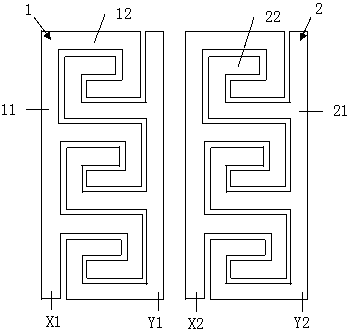

[0012] A single-layer capacitive electrode layout structure, including a substrate, on which are arranged a number of X electrodes 1 and Y electrodes 2 arranged in parallel in one direction, the X electrodes 1 are X1, X2..., and the Y The electrodes 2 are Y1, Y2..., and the electrode matching one X electrode 1 is the Y electrode 2. The X electrodes 1 and Y electrodes 2 are arranged in sequence, and are connected to the corresponding pins of the touch chip on the FPC. , and its bridging point is located on the FPC (Flexible Printed Circuit, flexible circuit b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com