Semiconductor device and method for accelerating erase verification procedure by the same

A verification program, semiconductor technology, applied in information storage, static memory, digital memory information, etc., can solve problems such as long erasure verification time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to fully understand the purpose, features and effects of the present invention, the present invention will be described in detail through the following specific embodiments and accompanying drawings, as follows.

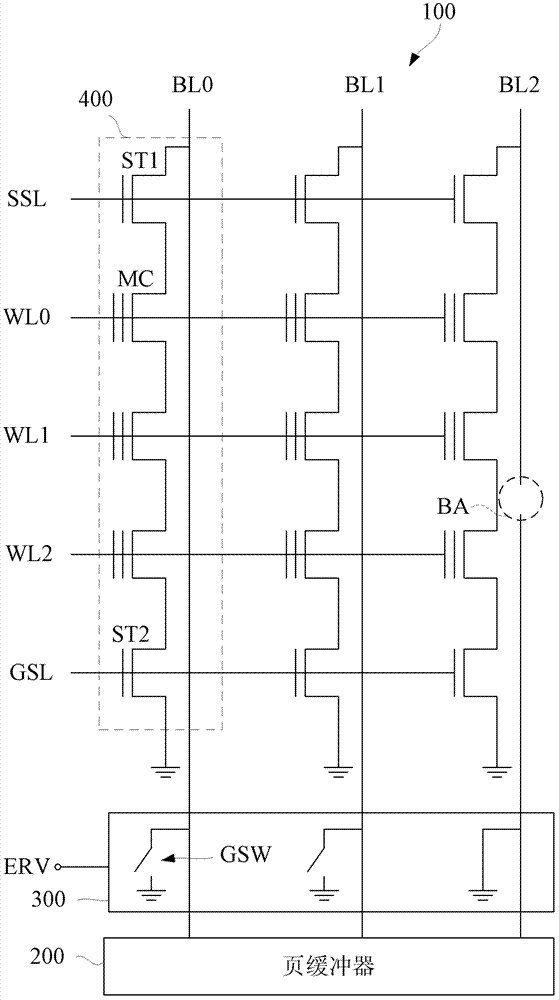

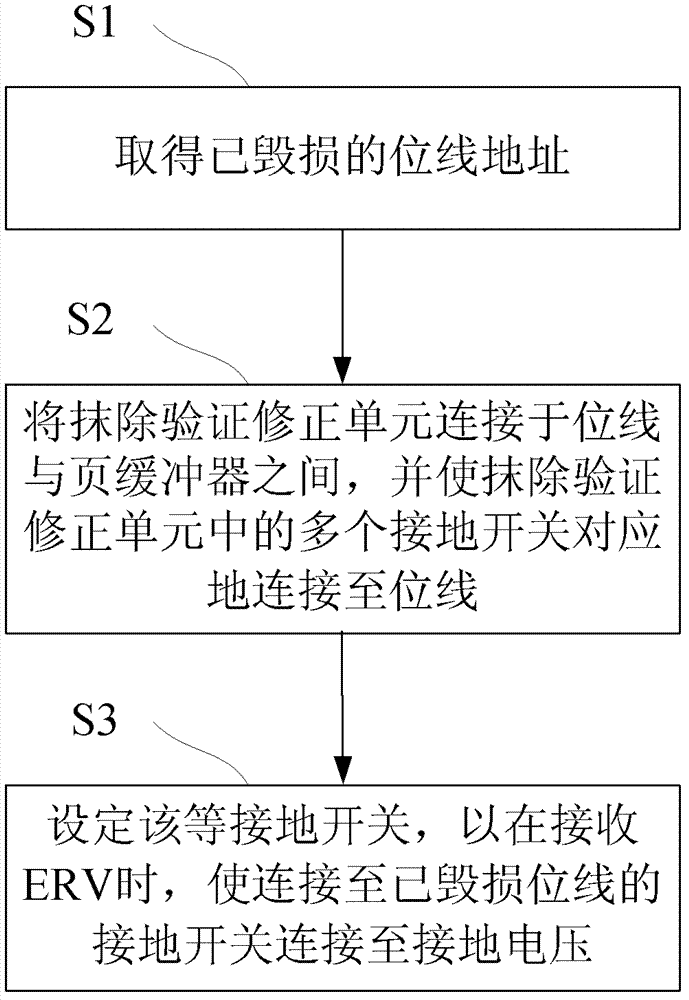

[0031] See first figure 1 , is a circuit block diagram of the NAND flash memory device in the semiconductor device of the embodiment of the present invention when it is in the erase verification state. The present invention takes a NAND flash memory device as an example, and other types of semiconductor devices, such as semiconductor devices such as transistors, are applicable to the device structures or methods proposed in the embodiments of the present invention.

[0032] figure 1 The memory cell array 100 of the present invention is an example of three NAND strings. In this example, each NAND string 400 includes a string selection transistor ST1, a ground selection transistor ST2, and three memory cells MC.

[0033] The memory cell array 100 incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com