A verification method of sram type fpga synchronous switching noise

A technology of synchronous switching noise and synchronous switching, which is applied in the direction of noise figure or signal-to-noise ratio measurement, etc., can solve problems such as synchronous switching noise, and achieve the effect of convenient comparison test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Specific embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0045] A kind of SRAM type FPGA synchronous switching noise verification method that the present invention proposes is based on following device and carries out:

[0046] Such as Figure 4 As shown, the SRAM type FPGA synchronous switching noise verification device includes: PC, FPGA socket, signal input unit and adjustable load capacitance;

[0047] PC: Provide configuration files for the FPGA to be verified and configure the FPGA through JTAG;

[0048] FPGA socket: provide an interface for the FPGA to be verified and the verification device;

[0049] Signal input unit: provide an input signal with adjustable edge rise / fall time for the FPGA to be verified;

[0050] Adjustable load capacitance: provide adjustable load capacitance for the FPGA to be verified.

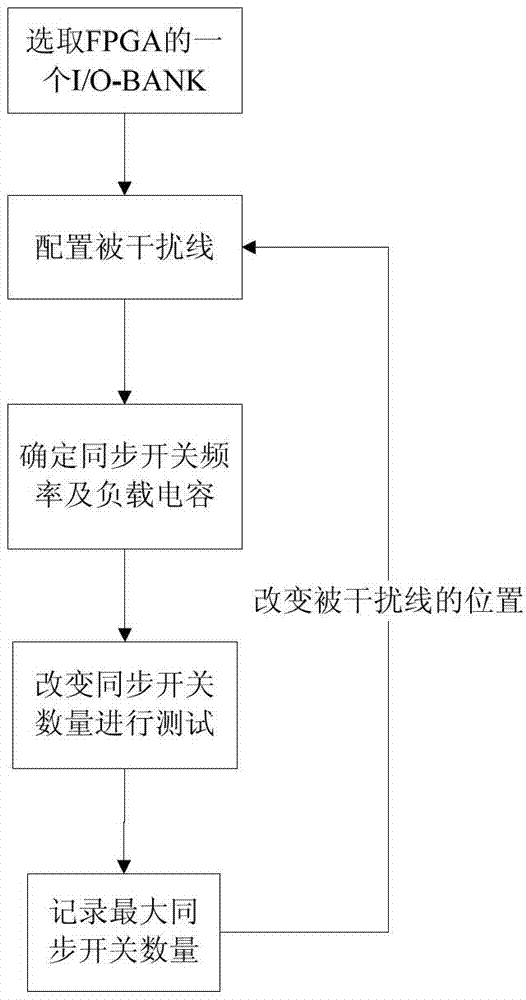

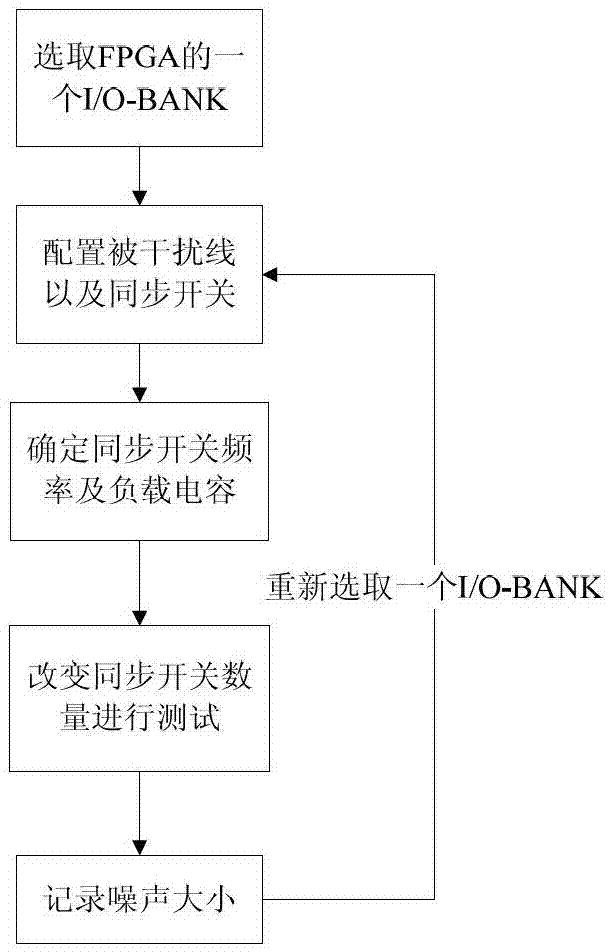

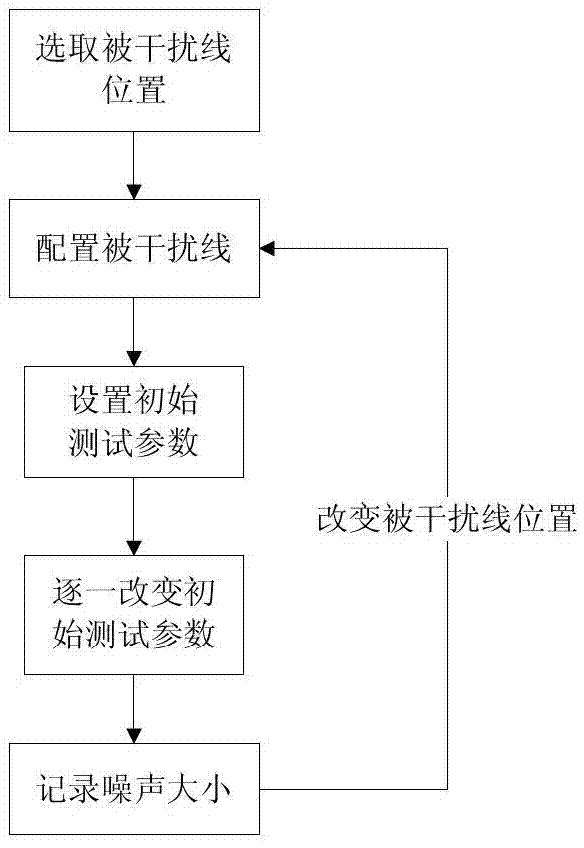

[0051] The SRAM type FPGA synchronous switching noise verification meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com