An optimal design method for electrical properties of optoelectronic integrated packaging structures

A technology of electrical performance optimization and packaging structure, applied in computing, electrical digital data processing, instruments, etc., can solve the problems of heavy workload, low efficiency, poor precision, etc., and achieve the effect of improving electrical performance, convenient use, and optimized design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] (1) Establish a three-dimensional geometric model of the package structure

[0020] Open the AnsoftHFSS interface (the version used is HFSS-9), use the HFSS software library to establish a three-dimensional geometric model of the adjacent pads of the package, and mark the pad diameter as 100um, the pad spacing as 40um, the substrate thickness as 300um, and the gap width as Structural parameters of 12um and signal line width of 100um.

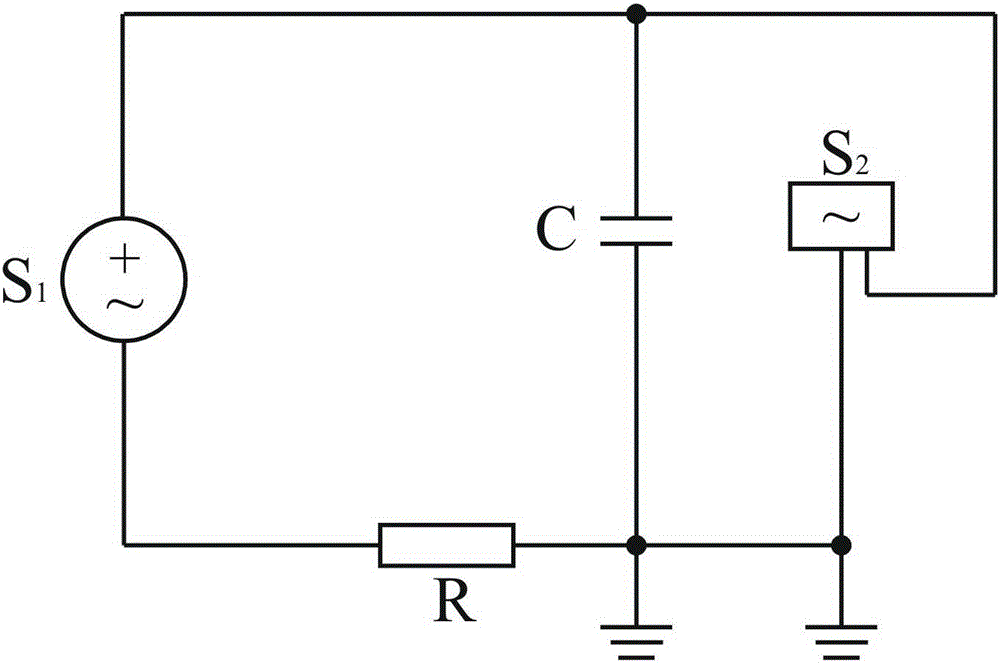

[0021] (2) Establish an RC equivalent circuit

[0022] See attached figure 1 , input the above three-dimensional geometric model parameters into the HFSS simulation software, and then use the finite element program of HFSS, combined with the geometric structure parameters of the package to capture the resistance R of the equivalent circuit is 46.52Ω, the capacitance C is 0.0125pF, the resistance R and capacitance C and AC signal source S 1 Form a series circuit and connect the oscilloscope S 2 Parallel to both ends of the capacitor C,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com