Chip sorting library and its pick-and-place mechanism and buffer area planning method for chip sorting library

A buffer area and chip technology, applied in storage devices, conveyor objects, transportation and packaging, etc., can solve problems such as poor scalability, increased load, complex layout, etc., and achieve high work efficiency, simple structure, and expanded capacity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be described in further detail below in conjunction with the embodiments and accompanying drawings, but the embodiments of the present utility model are not limited thereto.

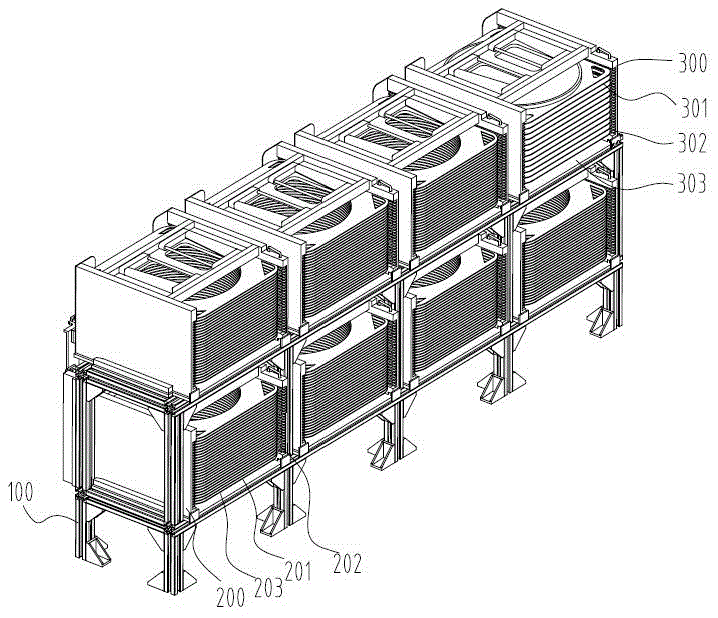

[0046] See figure 2 , the present invention provides a chip sorting library, comprising a bracket 100, a chip sorting cassette 200 and a chip storage cassette 300, the chip sorting cassette 200 and the chip storage cassette 300 are fixed on the bracket 100, and the chip sorting cassette 200 is set There is a slot 202 for fixing the chip sorting tray 201, and the chip sorting tray 201 is fixed in the chip sorting cassette 200 through the slot 202; the chip storage cassette 300 is provided with a slot 302 for fixing the chip storage tray 301, and the chip storage tray 301 is fixed in the chip storage cassette 300 through the card slot 302; the structure of the chip sorting cassette 200 is the same as that of the chip storage cassette 300, and the external dimensions of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com