Debugging multithreaded code

A technology for code and debugging applications, applied in the field of mechanisms, systems/devices that provide support for debugging multithreaded code, and can solve problems such as disrupting parallel program timing, masking errors, and being difficult to find.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

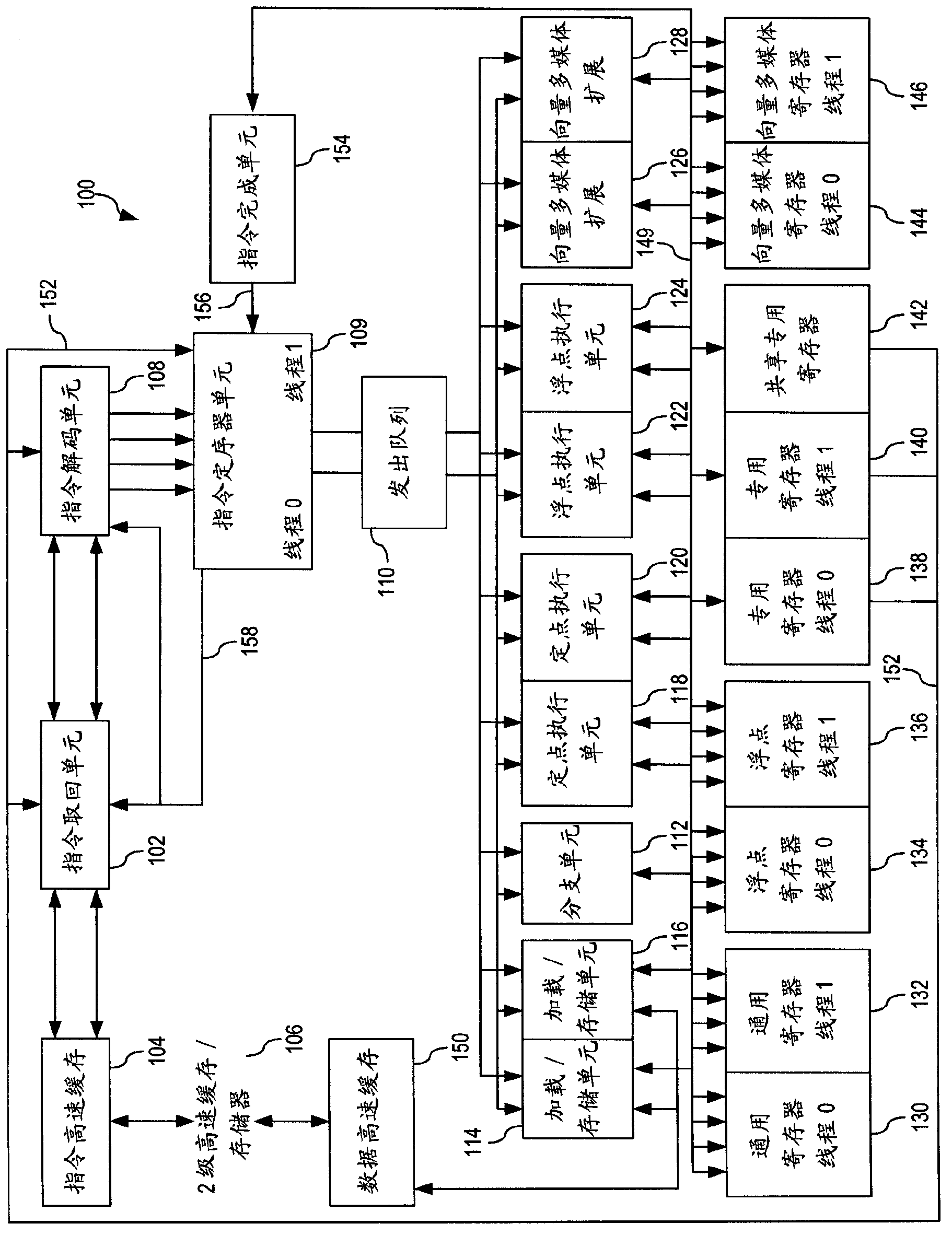

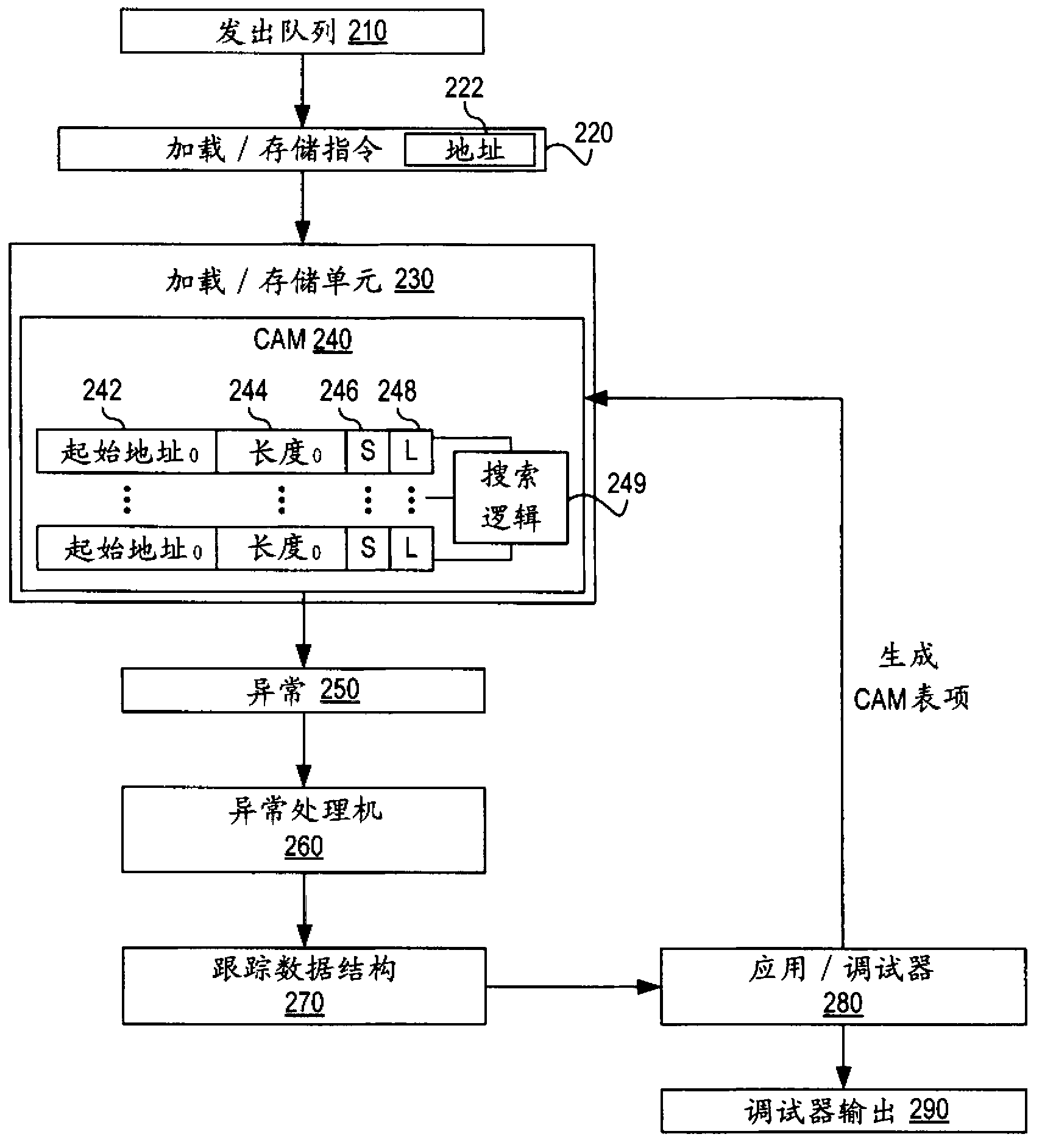

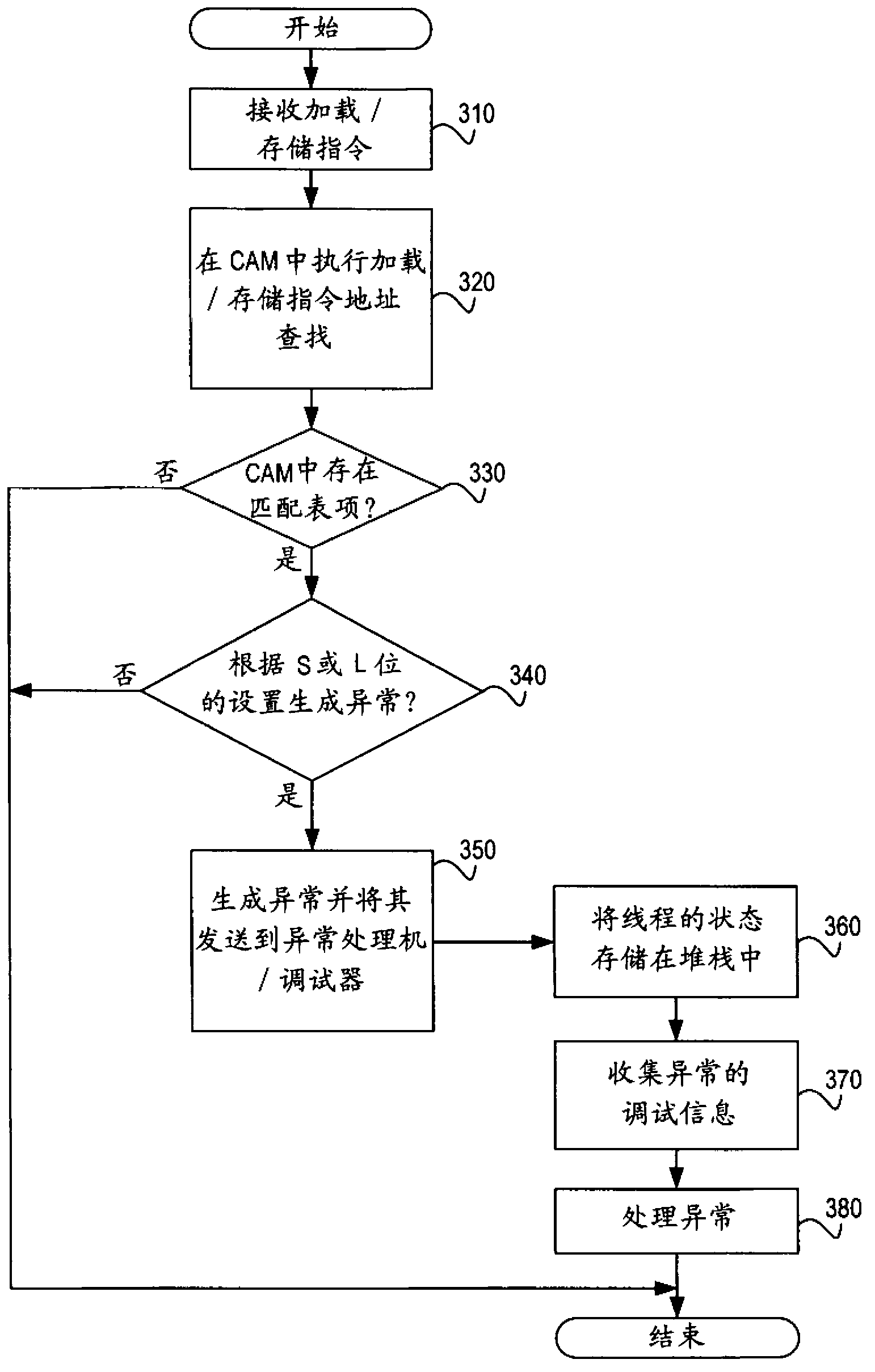

[0016] The exemplary embodiments provide a mechanism to provide debugging support for multi-threaded computer code. The mechanisms of the exemplary embodiments provide hardware support that enables applications to track memory accesses to multiple ranges in memory. The hardware support includes content addressable memory (CAM) structures, which can be set by the application or a debugger controlling the application. Each entry in the CAM structure has a start address, which specifies the start address of the monitored memory range. The entry also includes a length field, a storage bit (or S bit) and a load bit (or L bit), the length field specifies the size of the monitored memory range corresponding to the entry, the storage bit and A load bit enables detection of memory stores and loads, respectively, to the memory range defined by the start address and length.

[0017] At the hardware level, the processor checks every access to memory within a running thread. If the addr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com